A Triple-Modulus Frequency Divider with Embedded Switches in 90-nm CMOS Process

Yu-Sheng Lin,

Yeong-Her Wang and

Chun-Lin Lu

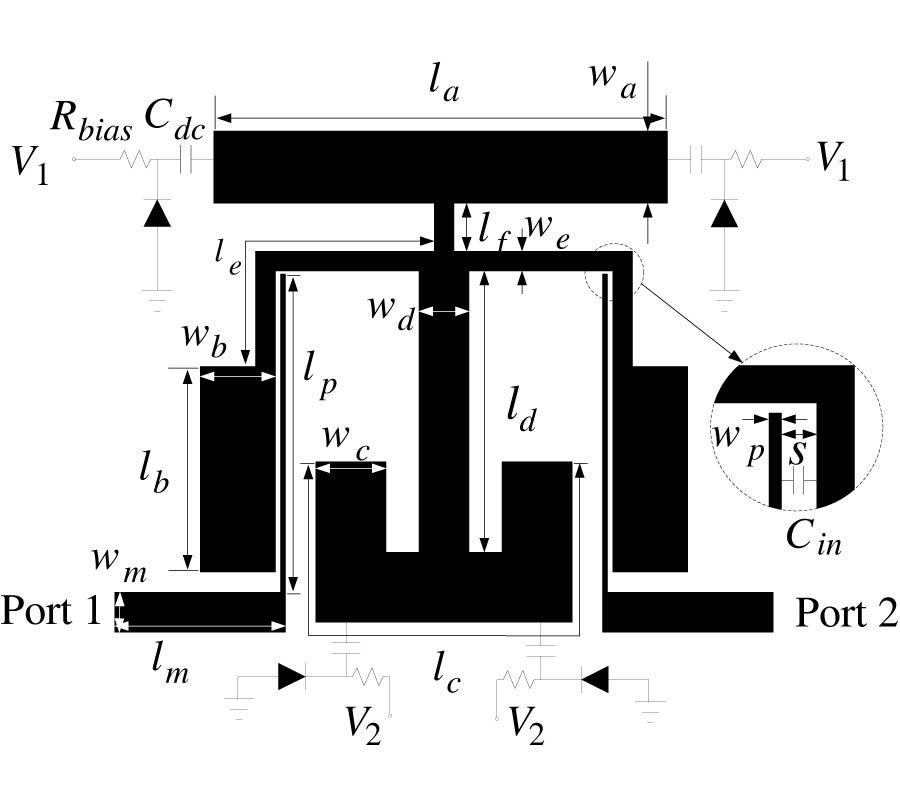

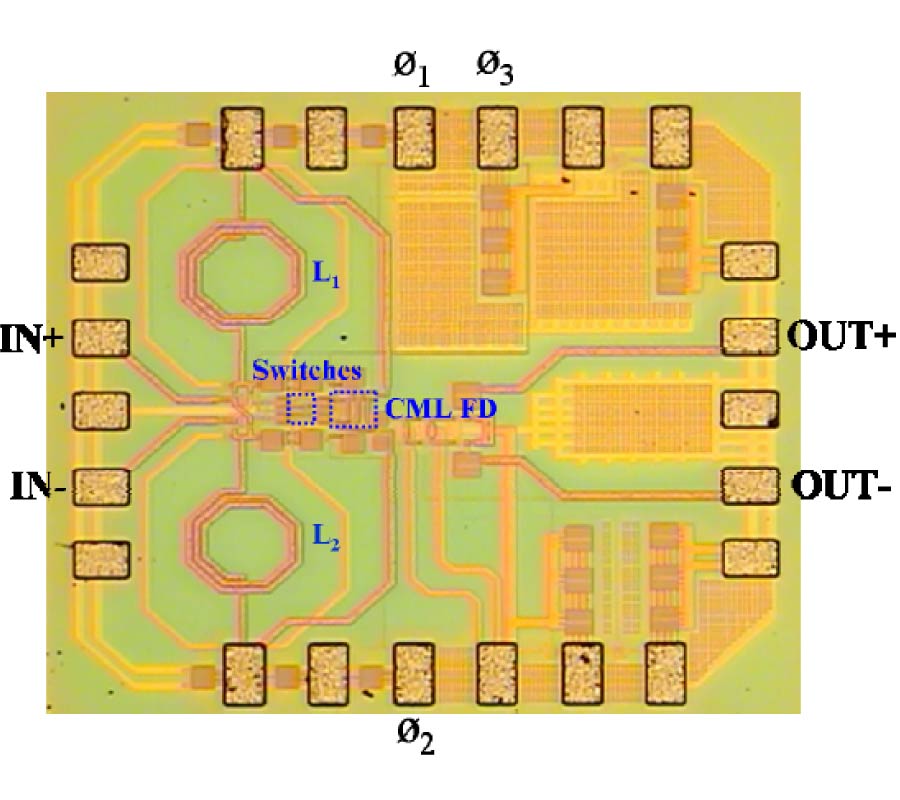

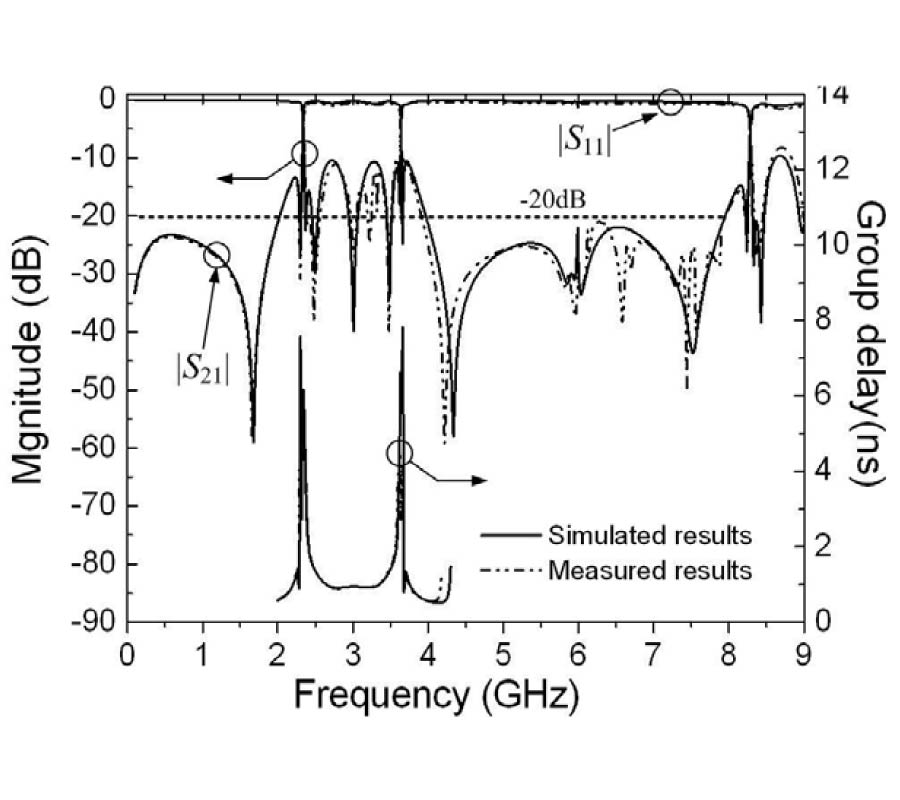

A high-speed triple-modulus frequency divider (FD) is designed and fabricated in a 90-nm CMOS process. With three pairs of nMOS switches inserted in the signal paths of the regenerative divider, the FD can offer three selectable division ratios of 1/2, 1/3, and 1/4. The corresponding behavior model of the proposed divider is utilized to explain the operation principle and analyze the locking range. From the experimental results, the divider consumes 6.8 mW of dc power from a 1.2-V supply voltage, and the locking ranges for the 1/2, 1/3, and 1/4 divide modes are 16-23.8, 12.3-18, and 16.8-22.8 GHz, respectively. The maximum input frequencies of 23.8, 18, and 22.8 GHz for the 1/2, 1/3, and 1/4 division modes are demonstrated that the divider is attractive for application to a frequency synthesizer.