Experimental Study and SPICE Simulation of CMOS Inverters LATCH-Up Effects Due to High Power Microwave Interference

Haiyang Wang

,

Jiayin Li

,

Hao Li

,

Kaiqi Xiao

and

Hong Chen

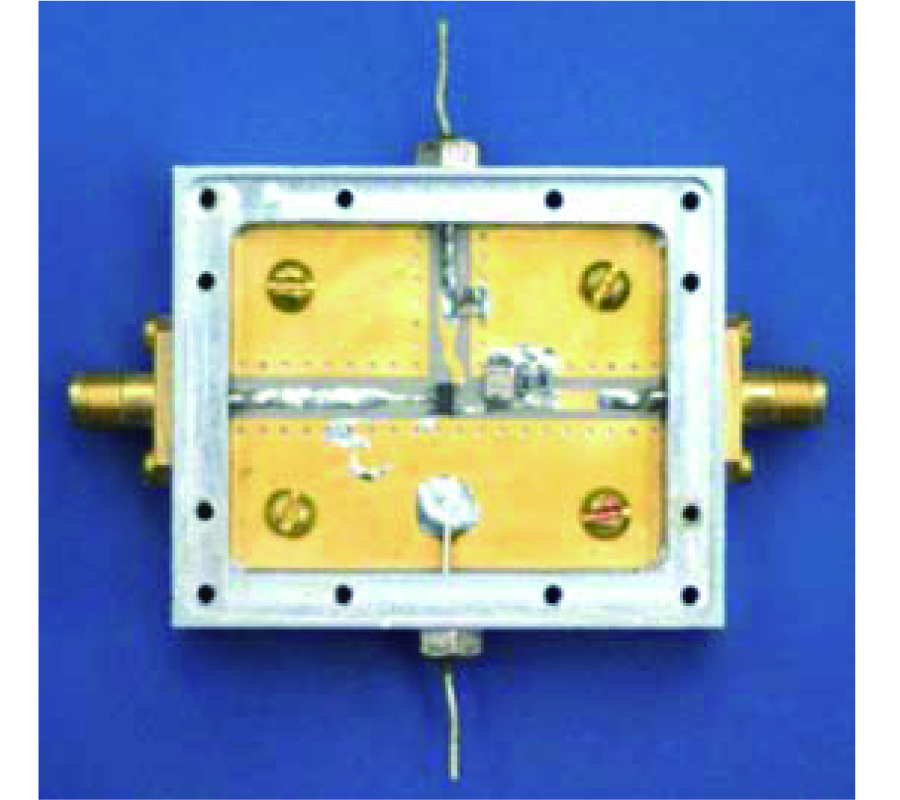

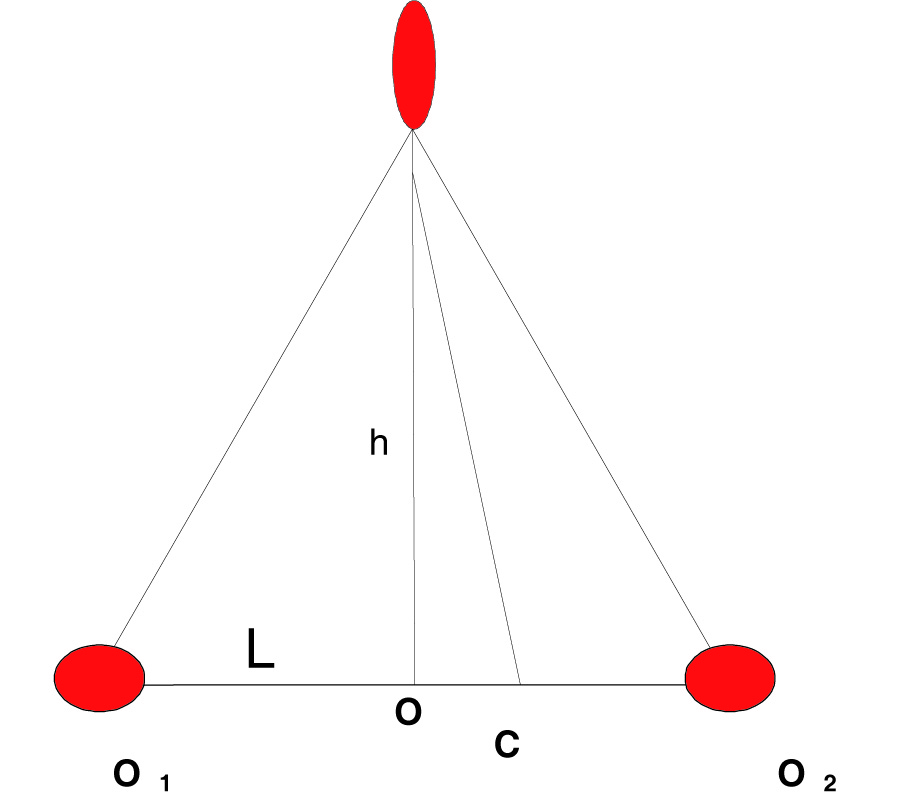

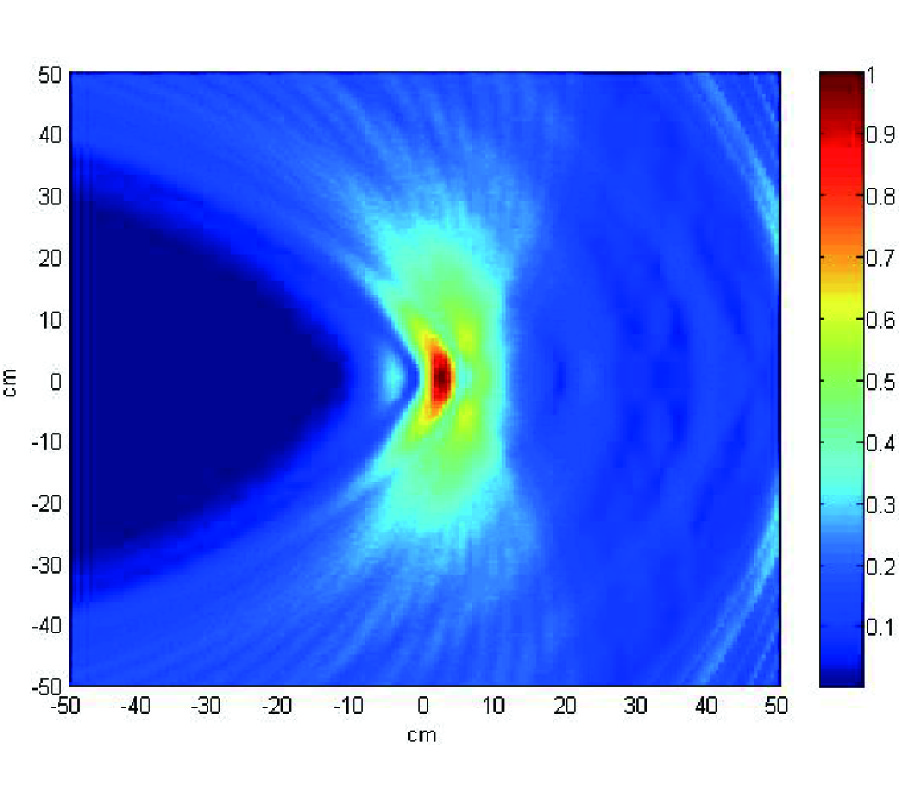

Experimental study and SPICE simulation of CMOS digital circuits latch-up effects due to high power microwave interference are reported in this paper. As a traditional inherent destruction phenomenon, latch-up effect may jeopardize the correct function of the circuits, and could be triggered in various ways such as ESD pulse, cosmic ray, heavy ion particles etc. Through the directly injected experimental investigation of CMOS inverters, it is shown that the single short high power RF pulse not only could disturb and upset the inverters output logic voltage, but also might trigger CMOS latch-up effects. It is observed that the RF pulse leading to inverters latch-up effects have energy threshold characteristics, which means that the injected RF pulse power is inversely proportional to the pulse width. SPICE simulations indicated that the inverters maximum static consumption current in latch-up state will increase up to 6600 multiples compared to the normal value when input logic state is high. With the device scaling down, higher integration and higher working frequency, the power consumption problem plays a significant role, which makes CMOS logic circuits more vulnerable due to the latch-up effects under high power microwave threats.