# A Design Oriented Linear Model for CRLH Distributed Oscillators

Giancarlo Bartolucci<sup>1, \*</sup>, Stefan Simion<sup>2</sup>, and Lucio Scucchia<sup>1</sup>

**Abstract**—The aim of this paper is to present a model for a Composite Right-/Left-Handed (CRLH) distributed oscillator. A linear approach is used for the analysis of the circuit. The effects of the losses and of the parasitic elements, both present in the active devices and in the passive components, are included. Analytic formulas for the design of the transmission lines used in the oscillator are given. The model is validated by means of a comparison with previously published measured data.

### 1. INTRODUCTION

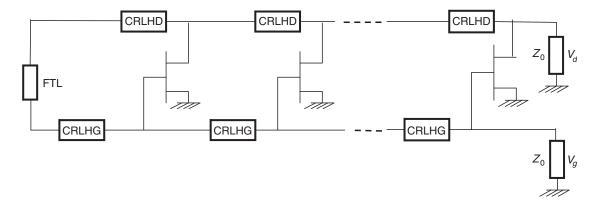

Distributed amplifier is an important wide-band element often used in microwave and millimeter wave systems [1–4]. The basic principle of this circuit has been also applied to other components, such as active dividers [5–7], frequency doublers [8–10], phase shifters [11–15], and oscillators [16–20]. For the latter ones the conventional configuration has been recently modified, replacing the low pass unit cell by a Composite Right-/Left-Handed (CRLH) topology [21, 22]. The conceptual configuration of this oscillator is shown in Fig. 1, where CRLHD and CRLHG are the drain and gate CRLH unit cells of the distributed amplifier, respectively. Each unit cell is composed by a series resonator and a parallel resonator, and for the transistor an ideal model can be assumed in this figure. Also, the drain and gate artificial lines of the distributed amplifier are connected by a feedback network (FTL) realized by means of a transmission line. As shown in [21], two output ports are available for this type of oscillator,

**Figure 1.** The distributed oscillator configuration composed by the feedback transmission line (FTL), the transistors, and the Composite Right-/Left-Handed cells termed CRLHD for the drain line and CRLHG for the gate line.

Received 22 May 2019, Accepted 18 July 2019, Scheduled 23 July 2019

<sup>\*</sup> Corresponding author: Giancarlo Bartolucci (bartolucci@eln.uniroma2.it).

<sup>&</sup>lt;sup>1</sup> Department of Electronic Engineering, University of Roma Tor Vergata, Via del Politecnico 1, Roma 00133, Italy. <sup>2</sup> Department of Electronics and Communications Engineering, Military Technical Academy, Bucharest 050141, Romania.

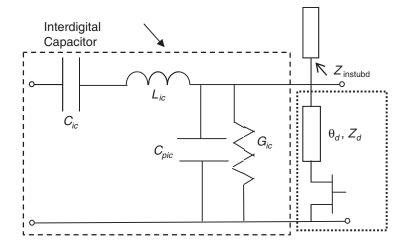

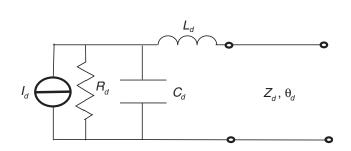

Figure 2. The unit cell of the drain line (CRLHD, taking into account the output impedance of the transistor).

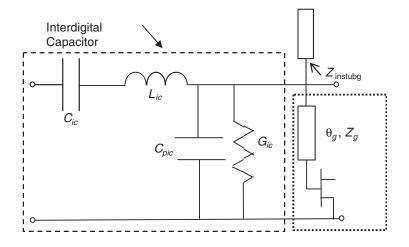

Figure 3. The unit cell of the gate line (CRLHG, taking into account the input impedance of the transistor).

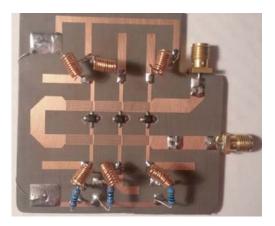

where similar power level may be obtained, with these output ports located at the ends of the drain and gate lines. In practice, CRLHD and CRLHG unit cells may be obtained using interdigital capacitors to realize the series resonators, while the parallel resonators are obtained using transmission lines, where the effects of parasitic capacitances of interdigital capacitors must be included. Taking into account the input and output equivalent circuits of the transistors, the circuit configurations for the CRLHD and CRLHG unit cells used in Fig. 1 behave more complicatedly, as shown in Fig. 2 and Fig. 3, respectively, where  $C_{ic}$ ,  $L_{ic}$ ,  $C_{pic}$ ,  $G_{ic}$  are elements of the interdigital capacitor equivalent circuit (here, the same for both unit cells). This oscillator has been designed and fabricated using MGF 4941AL InGaAs HEMTs, as presented in [21]. A photo of this circuit is presented in the same reference, but it is also shown here in Fig. 4 for the clarity of this paper, where the circuit elements of CRLHD and CRLHG unit cells may be observed.

In this paper, a linear approach is proposed for the characterization of this circuit. We can note that in literature this method of analysis has been at first applied to the standard distributed oscillator [16– 19], and after adopted in [21] also for the CRLH configuration. However, the analytic results presented in [21] have been obtained neglecting the following elements: the drain and gate resistors, which account for the losses in the transistor; the drain and gate inductors; the parasitic components of the CRLH passive cell. The purpose of this work is to develop a model for the oscillator which includes all

Figure 4. Photograph of the fabricated CRLH distributed oscillator which uses three active devices (N = 3) [22].

Figure 5. The model of the part of the drain line unit cell included in the dotted rectangle in Fig. 2. It is composed by the equivalent circuit of the drain of the transistor and by the connecting line with length  $\theta_d$ .

these effects, thus providing, in the general case, the analytic expression for the oscillation condition. Moreover, closed-form equations for the synthesis of the transmission lines utilized in the unit cell are derived.

The outline of the paper and the new contributions are listed below. In Sections 2 and 3 the models of the gate line and of the drain line are described, respectively. Section 4 is focused on the analysis of the feedback network, which is the key-element for transforming the distributed amplifier in an oscillator. Subsequently, the oscillation condition is imposed in the general case, including losses and parasitic effects. These analytic results are used in Section 5 for producing an innovative design procedure, which is the most important contribution of this work. In Section 6, some considerations on the power of the output signals are given. The validation of the presented approach is discussed in Section 7, where a comparison between predicted data and previously published experimental results is illustrated. Concluding remarks are provided in Section 8.

### 2. THE ANALYSIS OF THE DRAIN LINE

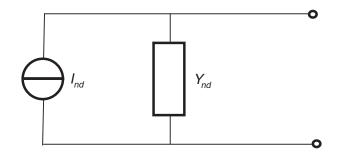

The equivalent circuit of the CRLHD unit cell is represented in Fig. 2. The transmission line of electrical length  $\theta_d$  is used to facilitate the physical connection of the transistor drain, inside the drain unit cell. The part of the cell included in the dotted rectangle is detailed in Fig. 5, where the equivalent circuit of the transistor drain together with the connecting transmission line is shown. This one port network can be characterized by means of the Norton's theorem, so obtaining the equivalent circuit depicted in Fig. 6. For the admittance  $Y_{nd}$  and the current  $I_{nd}$ , we have:

$$Y_{nd} = \frac{1}{Z_d} \frac{Z_d + j Z_{\text{LRC}} \text{tg}\theta_d}{Z_{\text{LRC}} + j Z_d \text{tg}\theta_d} \tag{1}$$

and

$$I_{nd} = \frac{I_d}{P_2 \cos \theta_d} \tag{2}$$

where:

$$Z_{\rm LRC} = j\omega L_d + \frac{R_d}{1 + j\omega C_d R_d} \tag{3}$$

and

$$P_2 = 1 + \left(j\omega L_d + jZ_d \operatorname{tg}\theta_d\right) \left(\frac{1}{R_d} + j\omega C_d\right) = |P_2| e^{j\psi_2} \tag{4}$$

Figure 6. The Norton model for the circuit in Fig. 5.

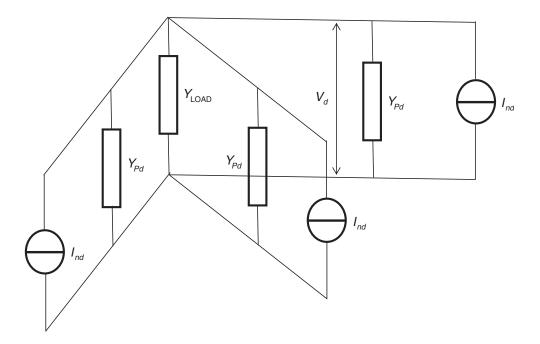

Figure 7. The equivalent network for the drain line.

Let's assume that the circuit composed by the inductor  $L_{ic}$  and the capacitor  $C_{ic}$  resonates at the oscillation frequency  $f_0$ . Hence it becomes a short circuit, and according to Figs. 2, 5, and 6, the unit cell can be modeled by the current generator  $I_{nd}$  and the admittance  $Y_{pd}$ , which is defined as follows:

$$Y_{pd} = Y_{nd} + j\omega_0 C_{pic} + \frac{1}{Z_{\text{instubd}}} + G_{ic}$$

(5)

where  $Z_{\text{instubd}}$  is the input impedance of the stub in the drain unit cell. Therefore, at the frequency of resonance  $f_0$ , for the whole drain line we can obtain the network shown in Fig. 7. The admittance  $Y_{\text{LOAD}}$  is obtained by adding the load admittance of the drain line, that is  $1/Z_0$ , to the input admittance of the feedback network loaded by the gate line.

# 3. THE ANALYSIS OF THE GATE LINE

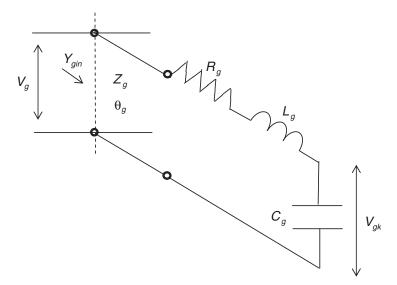

The equivalent circuit of the CRLHG unit cell is shown in Fig. 3. The transmission line of electrical length  $\theta_g$  has a similar role to the line of electrical length  $\theta_d$  used in the drain unit cell. It must be mentioned that the lines of electrical lengths  $\theta_g$  and  $\theta_d$  also ensure a separation between the gate and drain lines. In this way, the electromagnetic coupling between the two parts of the circuit is avoided. It is observed that the gate unit cell in this case has the same topology as that for the drain line (see

Figure 8. The model of the part of the gate line unit cell included in the dotted rectangle in Fig. 3. It is composed by the equivalent circuit of the gate of the transistor and by the connecting line with length  $\theta_q$ .

Fig. 2). The differences are in the value of the input impedance of the stub and in the electric parameters of the connecting line. The model of the elements included in the dotted rectangle is shown in Fig. 8, where the equivalent circuit of the transistor gate and the connecting line are present. For the input admittance  $Y_{gin}$  we find:

$$Y_{gin} = \left[ Z_g \frac{Z_{gk} + j Z_g \mathrm{tg} \theta_g}{Z_g + j Z_{gk} \mathrm{tg} \theta_g} \right]^{-1}$$

(6)

where  $Z_{qk}$  is given by:

$$Z_{gk} = j\omega L_g + \frac{1}{j\omega C_g} + R_g \tag{7}$$

The following relationship between  $V_{gk}$  and  $V_g$  can be written:

$$V_{gK} = P_4 V_g \tag{8}$$

where:

$$P_4 = \frac{1}{j\omega C_g \left( Z_{gk} \cos \theta_g + j Z_g \sin \theta_g \right)} = |P_4| e^{j\psi_4} \tag{9}$$

As for the drain line, the unit cell of the gate line is characterized by an admittance  $Y_{pg}$ , which is defined at  $f_0$  as:

$$Y_{pg} = Y_{gin} + j\omega_0 C_{pic} + \frac{1}{Z_{\text{instubg}}} + G_{ic}$$

(10)

where  $Z_{\text{instubg}}$  is the input impedance of the stub in the gate line unit cell.

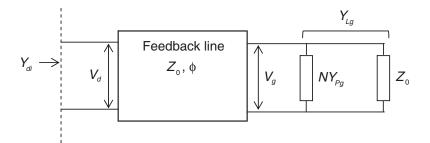

### 4. THE FEEDBACK NETWORK AND THE OSCILLATION CONDITION

A transmission line with characteristic impedance  $Z_0$  and electric length  $\phi_0$ , evaluated at  $f_0$ , is used for realizing the feedback network (see Fig. 1). If N is the number of unit cells, the load admittance of this feedback line, let say  $Y_{Lg}$ , is given by the load impedance of the gate line  $Z_0$  and by the admittances of the N cells, and the resulting circuit may be used to compute the input admittance into the feedback line,  $Y_{di}$ , given in Fig. 9. Thus, we have the following expression for  $Y_{Lg}$  and  $Y_{di}$ :

$$Y_{Lg} = \frac{1}{Z_0} + NY_{pg} \tag{11}$$

Figure 9. The feedback transmission line loaded by  $Z_0$  and by the N gate line unit cells.

and

$$Y_{di} = \left[ Z_0 \frac{1 + j Y_{Lg} Z_0 \operatorname{tg} \phi}{Z_0 Y_{Lg} + j \operatorname{tg} \phi} \right]^{-1}$$

(12)

The relationship between  $V_g$  and  $V_d$  can be expressed as:

$$V_g = V_d \left(\cos\phi - jZ_o Y_{di}\sin\phi\right) \tag{13}$$

$V_d$  can be calculated as the ratio of the current given by the N generators  $I_{nd}$  and the admittance obtained by adding  $Y_{\text{LOAD}}$  to  $NY_{pd}$ . Therefore:

$$V_d = \frac{-NI_{nd}}{NY_{pd} + Y_{\text{LOAD}}} = \frac{-N}{NY_{pd} + Y_{\text{LOAD}}} \frac{I_d}{P_2 \cos \theta_d}$$

(14)

where:

$$Y_{\text{LOAD}} = \frac{1}{Z_o} + Y_{di} \tag{15}$$

We assume for  $I_d$ :

$$I_d = g_m V_{gK} = g_m P_4 V_g \tag{16}$$

By substituting Equation (16) in Equation (14), we obtain:

$$V_d = \frac{-N}{NY_{pd} + Y_{\text{LOAD}}} \frac{g_m P_4 V_g}{P_2 \cos \theta_d} \tag{17}$$

From Eqs. (17) and (13) one then has:

$$1 = \frac{-Ng_m P_4}{P_2 \cos \theta_d} \frac{(\cos \phi - jZ_o Y_{di} \sin \phi)}{NY_{pd} + Y_{\text{LOAD}}}$$

(18)

This equation is the oscillation condition for the CRLH distributed oscillator.

# 5. THE DESIGN PROCEDURE OF THE CRLH OSCILLATOR

We can note that neglecting the losses in the two stubs, their input impedances  $Z_{\text{instubd}}$  and  $Z_{\text{instubg}}$  are imaginary numbers. By using Equations (5) and (10), let us impose the following conditions at the oscillation frequency  $f_0$ :

$$j \operatorname{Im}\left[Y_{pd}\right] = j \operatorname{Im}\left[Y_{nd}\right] + j \omega_0 C_{pic} + \frac{1}{Z_{\text{instubd}}} = 0$$

(19)

$$j \operatorname{Im}\left[Y_{pg}\right] = j \operatorname{Im}\left[Y_{gin}\right] + j \omega_0 C_{pic} + \frac{1}{Z_{\text{instubg}}} = 0$$

<sup>(20)</sup>

Equations (19) and (20) can provide the values of  $Z_{\text{instubd}}$  and  $Z_{\text{instubg}}$ , thus allowing the design of the two stubs. As a consequence of Eqs. (19) and (20), the admittances  $Y_{pd}$ ,  $Y_{pg}$  are real and become:

$$Y_{pd} = \operatorname{Re}\left[Y_{nd}\right] + G_{ic} \tag{21}$$

$$Y_{pg} = \operatorname{Re}\left[Y_{gin}\right] + G_{ic} \tag{22}$$

#### Progress In Electromagnetics Research M, Vol. 83, 2019

Let's introduce parameters  $B, D, \psi$ :

$$B = Z_0 N Y_{pg} \tag{23}$$

$$D = \sqrt{[NY_{pd} + (2+B)Y_o]^2 + NY_{pd}B[(2+B)(NY_{pd} + 2Y_o)]\sin\phi^2}$$

(24)

$$\psi = \arctan\left[ tg\phi \frac{(1+B)(NY_{pd} + Y_o) + Y_o}{NY_{pd} + (2+B)Y_o} \right]$$

(25)

so that the oscillation condition (18) can be written as:

$$1 = \frac{-Ng_m |P_4| e^{j\psi_4}}{De^{j\psi} |P_2| e^{j\psi_2} \cos\theta_d}$$

(26)

which gives:

$$\psi = -\psi_2 + \psi_4 + \pi \tag{27}$$

and

$$g_m = \frac{D \left| P_2 \right| \cos \theta_d}{N \left| P_4 \right|} \tag{28}$$

According to Eq. (25), the unknown  $\phi$  is related to the phase  $\psi$  as follows:

$$\phi = \arctan\left[ \operatorname{tg} \psi \frac{NY_{pd} + (2+B)Y_o}{(1+B)(NY_{pd} + Y_o) + Y_o} \right]$$

(29)

The phase  $\phi$  must be inserted in Eq. (24) for obtaining D, which in turn can be utilized in Eq. (28) for computing  $g_m$ .

In conclusion, the design steps of the distributed oscillator can be briefly summarized as follows:

<u>Step1</u>: The interdigital capacitor is designed by means of an electromagnetic simulator, imposing  $f_0$  as resonance frequency. Hence, the values of the capacitance  $C_{pic}$  and of the conductance  $G_{ic}$  are also calculated.

<u>Step2</u>: The two transmission lines used for connecting the transistor to the passive elements of the unit cells are synthesized, choosing the electric lengths  $\theta_d$  and  $\theta_g$  in such a way to avoid unwanted coupling effects between the gate and drain lines.

<u>Step3</u>: The bias point in the characteristic curves of the transistor is selected. As a consequence of this choice, the values of  $L_d$ ,  $L_g$ ,  $C_d$ ,  $C_g$ ,  $R_d$ , and  $R_g$  are obtained.

Step4: The two stubs are designed by using the values of  $Z_{\text{instubd}}$  and  $Z_{\text{instubg}}$  provided by Eqs. (19) and (20).

Step5: The electric length  $\phi$  is utilized for computing the geometric length of the feedback transmission line.

### 6. CONSIDERATIONS ON THE POWER OF THE OUTPUT SIGNALS

The distributed oscillator shown in Fig. 1 has two output ports, hence it provides two sinusoidal signals. The linear model presented in this paper does not allow to calculate the powers of these signals, respectively  $P_g$  and  $P_d$ . However, it yields an analytic formula for the ratio of these two powers, which is related to the difference between their values in dBm,  $P_{gdBm}$  and  $P_{ddBm}$ . The expressions of  $P_{gdBm}$  and  $P_{ddBm}$  can be written as:

$$P_{gdBm} = 10 \log P_g = 10 \log \frac{|V_g|^2}{2Z_0 10^{-3}}$$

(30)

$$P_{ddBm} = 10 \log P_d = 10 \log \frac{|V_d|^2}{2Z_0 10^{-3}}$$

(31)

Thus we have for the difference of the output powers  $\Delta P_{\rm dBm}$ :

$$\Delta P_{\rm dBm} = P_{d\rm dBm} - P_{g\rm dBm} = 10 \log \frac{|V_d|^2}{|V_g|^2}$$

(32)

According to Eq. (13), we find:

$$\left|\frac{V_d}{V_g}\right|^2 = 1 + \sin\phi^2 \left(2 + B\right) B \tag{33}$$

From Eqs. (32) and (33), we obtain for  $\Delta P_{\rm dBm}$ :

$$\Delta P_{\rm dBm} = 10 \log \frac{|V_d|^2}{|V_q|^2} = 10 \log \left[1 + \sin \phi^2 \left(2 + B\right) B\right]$$

(34)

# 7. COMPARISON WITH EXPERIMENTAL RESULTS

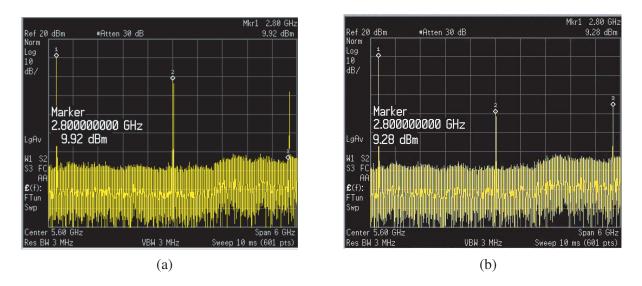

The numerical results obtained by using the proposed linear approach have been compared to the experimental results presented in [22]. The values of its equivalent circuit elements are listed in Table 1. In particular,  $L_d$ ,  $L_g$ ,  $C_d$ ,  $C_g$ , and  $R_g$  have been obtained in [23], whereas  $R_d$  is as usual computed as the inverse of the slope of the current-voltage characteristics  $(I_d-V_d)$  at the operating point. In Table 1, the values of  $C_{pic}$  and  $G_{ic}$  are also reported, both achieved by the electromagnetic simulation of the interdigital capacitor. For this purpose, the Momentum simulator implemented in the Advanced Design System (ADS) — Keysight software package has been utilized. Moreover, in Table 1 the values of characteristic impedances  $Z_d$ ,  $Z_g$  and the values of electrical lengths  $\theta_d$  and  $\theta_g$  are given. For this oscillator, the measured frequency spectra at the drain and gate line outputs are presented in Fig. 10 [22]. Using these experimental results,  $\Delta P_{dBm} = 0.64 \text{ dBm}$  is obtained. In Table 2, the values for  $\Delta P_{dBm}$  and  $\phi$  (evaluated at the oscillation frequency  $f_0 = 2.8 \text{ GHz}$ ) are computed by using the formulas developed in this paper, in comparison with the results provided by the simplified analysis [21] and with the experimental values measured for the realized circuit [22]. From Table 2, the following considerations can be inferred:

- The length of the feedback line for the manufactured oscillator is smaller than the value predicted in [21]. The proposed approach yields an electric length quite close to the value of the realized circuit.

- By using the simplified analysis in [21], the same power is expected for the two output signals. However, the measured values are not equal. This difference is mostly accounted in the described model. It is worth adding that in the model the losses in the feedback line and the stubs are not included. This approximation can explain the existing small discrepancy in Table 2.

Figure 10. Measured frequency spectra at the two outputs of the oscillator: (a) drain line output and (b) gate line output.

# Table 1.

| Parameters               | Values                |  |  |

|--------------------------|-----------------------|--|--|

| $L_d$ (nH)               | 1                     |  |  |

| $L_g$ (nH)               | 0.45                  |  |  |

| $C_d (\mathrm{pF})$      | 0.16                  |  |  |

| $C_g (\mathrm{pF})$      | 0.43                  |  |  |

| $R_d (\Omega)$           | 250                   |  |  |

| $R_g (\Omega)$           | 18                    |  |  |

| $C_{pic} (\mathrm{pF})$  | 0.64                  |  |  |

| $G_{ic} \ (\Omega^{-1})$ | $0.733 \cdot 10^{-3}$ |  |  |

| $Z_d \ (\Omega)$         | 107                   |  |  |

| $Z_g (\Omega)$           | 107                   |  |  |

| $	heta_d$ (°)            | 18.6                  |  |  |

| $	heta_g$ (°)            | 6.2                   |  |  |

Table 2.

| Parameters               | $\phi$ (deg.) | $\Delta P_{\rm dBm}$ |

|--------------------------|---------------|----------------------|

| Simplified analysis [21] | 180°          | 0                    |

| Realized Circuit [22]    | $138^{\circ}$ | 0.64                 |

| This work                | $158^{\circ}$ | 0.41                 |

### 8. CONCLUSION

A linear model for the CRLH distributed oscillator has been proposed. An analytic expression for the oscillation condition has been obtained. The model includes most of the losses present in the structure. Moreover, it provides a general design procedure for this kind of circuit. A comparison with experimental results for a previously realized oscillator confirms the validity of the presented approach.

# REFERENCES

- Lin, Y.-S., J.-F. Chang, and S.-S. Lu, "Analysis and design of CMOS distributed amplifier using inductively peaking cascaded gain cell for UWB systems," *IEEE Trans. Microwave Theory Techn.*, Vol. 59, No. 10, 2513–2524, 2011.

- Entesari, K., A. R. Tavakoli, and A. Helmy, "CMOS distributed amplifiers with extended flat bandwidth and improved input matching using gate line with coupled inductors," *IEEE Trans. Microwave Theory Techn.*, Vol. 57, No. 12, 2862–2871, 2009.

- Bartolucci, G., F. Giannini, and L. Scucchia, "Design considerations for the gate circuit in distributed amplifiers," *IET Circuits Devices Systems*, Vol. 4, No. 3, 181–187, 2010.

- Guan, X. and C. Nguyen, "Low-power-consumption and high-gain CMOS distributed amplifiers using cascade of inductively coupled common-source gain cells for UWB systems," *IEEE Trans. Microwave Theory Techn.*, Vol. 54, No. 8, 3278–3283, 2006.

- 5. Lo, W. K. and W. S. Chan, "Broadband integrated active divider and combiner based on distributed amplification," *Electronics Letters*, Vol. 44, No. 13, 779–780, 2008.

- Safarian, A., L. Zhou, and P. Heydari, "CMOS distributed active power combiners and splitters for multi-antenna UWB beamforming transceivers," *IEEE J. Solid-State Circuits*, Vol. 42, No. 7, 1481–1491, Jul. 2007.

- Testa, P. V., C. Carta, and F. Ellinger, "Analysis and design of a 220-GHz wideband SiGe BiCMOS distributed active combiner," *IEEE Trans. Microw. Theory Techn.*, Vol. 64, No. 10, 3049–3059, Oct. 2016.

- Carman, E., M. Case, M. Kamegawa, R. Yu, K. Giboney, and M. J. W. Rodwell, "V-band and W-band broadband, monolithic distributed frequency multipliers," *IEEE Microwave Guided Wave Lett.*, Vol. 2, 253–254, 1992.

- Tang, Y. L., P.-Y. Chen, and H. Wang, "A broadband PHEMT MMIC distributed doubler using high-pass drain line topology," *IEEE Microwave and Wireless Components Lett.*, Vol. 14, No. 5, 201–203, May 2004.

- 10. Simion, S. and G. Bartolucci, "Distributed amplifier based broadband and low spurious frequency doubler," *Romanian Journal of Information Science and Technology*, Vol. 20, No. 4, 331–341, 2017.

- 11. Hung, J. J., L. Dussopt, and G. M. Rebeiz, "Distributed 2- and 3-bit W-band MEMS phase shifters on glass substrates," *IEEE Trans. Microwave Theory Techn.*, Vol. 52, No. 2, 600–606, 2004.

- 12. Bartolucci, G., "Image parameter modeling of analog traveling-wave phase shifters," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, Vol. 49, No. 10, 1505–1509, 2002.

- Topali, K., O. A. Civi, S. Demir, S. Koc, and T. Akin, "A monolithic phased array using 3-bit distributed RF MEMS phase shifters," *IEEE Trans. Microwave Theory Techn.*, Vol. 56, No. 2, 270–277, 2008.

- Du, Y., J. Bao, and X. Zhao, "5-bit MEMS distributed phase shifter," *Electronics Letters*, Vol. 46, No. 21, 1452–1453, 2010.

- Bartolucci, G., S. Catoni, F. Giacomozzi, R. Marcelli, B. Margesin, and D. Pochesci, "Realisation of distributed RF MEMS phase shifter with very low number of switches," *Electronics Letters*, Vol. 43, No. 23, 1290–1292, 2007.

- 16. Skvor, Z., S. R. Saunders, and C. S. Aitchison, "Novel decade electronically tunable microwave oscillator based on the distributed amplifier," *Electronics Letters*, Vol. 28, No. 17, 1647–1648, 1992.

- 17. Divina, L. and Z. Skvor, "The distributed oscillator at 4 GHz," *IEEE Trans. Microwave Theory Techn.*, Vol. 46, No. 12, 2240–2243, 1998.

- Wu, H. and A. Hajimiri, "Silicon-based distributed voltage-controlled oscillators," *IEEE Journal of Solid-State Circuits*, Vol. 36, No. 3, 493–502, 2001.

- Aku, M. O. and R. S. Imam, "Silicon bipolar distributed oscillator design and analysis," *Science World Journal*, Vol. 9, No. 4, 29–38, 2014.

- Bhattacharyya, K., "Tunable distributed harmonic voltage controlled oscillator for generating second and third harmonic microwave signals in 180 nm CMOS," *International Conference on* VLSI Systems, Architectures, Technology and Applications (VLSI-SATA), 1–4, 2016.

- Simion, S. and G. Bartolucci, "High power efficiency distributed oscillator based on compositeright-/left-handed unit cells," *Appl. Phys. Lett.*, Vol. 107, 104102, 2015.

- Bartolucci, G., S. Simion, and L. Scucchia, "Power performance and spurious frequencies analysis of composite right-/left-handed (CRLH) distributed oscillators," *Progress In Electromagnetics Research Letters*, Vol. 75, 67–73, 2018.

- Simion, S. and G. Bartolucci, "Design considerations and experimental results on composite right-/left-handed based distributed oscillator," *International Conference on Computer as a Tool*, (EUROCON 2015), 1–6, Salamanca, Spain, September 8–11, 2015.