## CRITICAL MODEL COMPONENTS AND THEIR FIN-GERPRINT FEATURES IN THE SIMULATED CON-DUCTED RADIO FREQUENCY IMMUNITY OF COM-PLEX INTEGRATED CIRCUITS

## Tao Su, Yehua Yang, and Zixin Wang<sup>\*</sup>

School of Physics and Engineering, Sun Yat-sen University, Guangzhou 510275, China

**Abstract**—To analyze and to handle the radio frequency immunity of microcontrollers requires understanding the origins of the complex frequency response of the immunity. This paper assumes that the frequency response of the immunity can be characterized with a set of fingerprint features in the immunity curves. Positions and shapes of those fingerprint features are determined by certain components in the disturbance propagation network. In order to prove that assumption, a series of models are created and simulated. The roles of various model components on the immunity are analyzed by comparing the simulation results from different model structures. The fingerprint features on the immunity curves are identified. The paper shows how to treat a wide-range immunity curve with separated features. It also shows the responsible model components for those separated features. With the awareness of those features and their origins, researchers can concentrate on extracting the models of the most important components in the disturbance propagation network when modeling the immunity of the complex integrated circuits like microcontrollers.

### 1. INTRODUCTION

The conducted radio frequency (RF) electromagnetic immunity, shortened as 'immunity', of integrated circuits (ICs) is the response of ICs to electromagnetic interference (EMI) signals in RF range through conducted channels. It is a common issue for most electronic systems. The measurement result of the immunity is the relationship between the maximal incident EMI power, under which an IC can still perform

Received 2 April 2013, Accepted 29 April 2013, Scheduled 19 May 2013

<sup>\*</sup> Corresponding author: Zixin Wang (wangzix@mail.sysu.edu.cn).

in a normal way, and the EMI frequency [1]. The immunity of ICs is a hybrid subject of microelectronics and RF electromagnetics. There are three fundamental topics in this subject: immunity tests, immunity modeling, and immunity mechanism. The immunity simulation is interesting because it is the only method to evaluate the immunity performance of ICs and electronic modules in the early design stage before the hardware comes out. Motivated by the IC industry, the international electric committee (IEC) has started to establish a standard for the modeling of the immunity of ICs [2].

The direct power injection (DPI) method has been applied to measure the immunity of IC since the earliest research on the IC EMI in 1970s [3]. It is widely accepted in the electronic industry [4] and is now included in the IEC standard [5]. This paper is dedicated to simulate the DPI immunity.

Complex ICs like center processing units, system on chips, and microcontrollers are nowadays key devices in electronic systems. Due to the huge number of transistors and complex geometries of interconnections of complex ICs, it is impractical to simulate the full IC using electromagnetic simulator at the field level or using SPICE simulator at the transistor level. Moreover, a complex IC can be configured in various ways, for example, with various system clock frequencies. The electrical property of a complex IC changes when the configuration changes. The amount of time to simulate the complex IC with all possible configurations is not acceptable. The immunity modeling of the complex ICs requires a great simplification on the IC without the loss of any important information of the IC.

Starting from early 2000s, several individual cases on the modeling of complex ICs for immunity simulations have been reported. Some of the simulation cases have used the statistical approach [6], the macromodel approach [7], and the neural network approach [8]. However, the most widely used approach uses the SPICE-formatted equivalent circuit [9–18]. [9–18] are performed on various types of pins of complex ICs. They cover issues like simulation setup, the model of the test fixture, the core model, and the package model. To standardize the immunity model of complex ICs, there are still a lot to do. As is mentioned in the previous paragraph, the circuit of the IC needs simplification, and the boundary of the simplification is so far not clear. The fundamental question, i.e., what is the right structure of the IC model and the model contents, has not been answered.

The purpose of this paper is neither to add a new study case with a specific complex IC nor to propose a new structure for a standard model. It is mainly intended to find the right format of a standard model and the necessary (not complete) components that should be included into that standard model.

An immunity model of an IC system contains two groups: the EMI propagation networks (EMIPNs) and the on-chip functional modules (OCFMs). Both the DPN transfer coefficient and the OCFM responses could be frequency dependent. The OCFM response is not well understood and it requires deep investigation. The EMIPN is formed by the on-board, on-package, and on-chip coupling devices, loading devices, and interconnections. In most design procedures of complex ICs, standard cells and macro-modules are used, the main work of designers are the floorplan and routing. That is to say, the main work is constructing the EMIPN not building the transistor circuits. The same story happens for board designers and package designers. As a consequence, the EMIPN is the modification object for the immunity optimization of the IC. The frequency response of the EMIPN and the model of the EMIPN are important and are worth of special study.4 This paper is focused on the EMIPN. For OCFMs, only their impedance will be considered. The frequency response of OCFM is assumed to be constant. A model component is the representation of a physical channel in the EMIPN. The paper examines the following physical channels:

- Board devices,

- Package,

- Chip,

- Connecting Traces, polygons and planes,

- Inter-power domain coupling,

- Chip-board coupling,

- Package-board coupling,

- IO module.

A model component forms a path for the EMI current. It influences the propagation of the EMI signal from the EMI source to the OCFMs and thus influences the immunity of the IC. A frequency response curve is a two-dimension geometric structure. It can be decomposed into a set of fundament shapes. Those basic shapes can be marked as features. A model component influences the immunity through those features. This paper considers the following features of an immunity-frequency curve.

- Roll-off region,

- Roll-up region,

- Flat region,

- Corner,

- Peak,

- Dip.

In a SPICE netlist, each physical channel has its corresponding equivalent circuit. The equivalent circuit can be easily manipulated. which makes the SPICE format model especially suitable for immunity mechanism analysis. The model of this paper is in the SPICE format. The DPI immunity test method covers the frequency range from  $10^5$  Hz to  $10^9$  Hz. When the equivalent circuit of a physical channel is extracted, only the property dominating the behavior in the DPI frequency range is counted. The equivalent circuits in this paper take simple forms. The circuit elements are assigned with estimated typical values that are not from a particular IC system. That kind of estimation is not enough to match immunity measurement results; however, it is sufficient for the mechanism analysis. A model component can be linear or nonlinear. This paper leaves the nonlinear effects as in following-up work. As a summary, the models in this paper are SPICE netlist employing only linear elements that represent the main behaviors of the corresponding physical objects in frequency range from  $10^5$  Hz to  $10^9$  Hz.

A complex IC has multiple pins. Those pins can be roughly grouped into power supply pins and the input and/or output (IO) pin. According to the types of the signals, the IO pins can be grouped into data IO (DIO) pins and oscillator IO (XIO) pins. EMI signals can be injected to those pins with the ground pin as the reference. This paper studies the immunity of the power supply pin, the DIO pin, and the XIO pin. The signal propagation of an IC with its board follows two networks. The power components, supply pins and its interconnections form the power distribution network PDN. The PDN may have more than one domain. The IO pin, its load and the interconnections form an IO network (ION). The ION has two blocks, one for DIO and the other for the XIO. The model of IC and its PCB is called the device under test (DUT) model. The model with purely PDN network is the PDN model, labeled with P. The model with ION plus a perfect PDN is the IO model, labeled with SD for the data IO module and SX for the oscillator IO module. The whole model for immunity simulation consists of the test-fixture model and the DUT model.

Section 2 creates a series of models. It starts with a simple PDN model. New components in the PDN are added to the model step by step. After that, IO models are considered. The final DUT mode contains two power domains, a DIO block and an XIO block. Section 3, gives the methods for calculating the immunity. It illustrates the principles of formation of the critical features in the immunity. Section 4 shows the simulation results on

### Progress In Electromagnetics Research, Vol. 139, 2013

the aforementioned models. The impacts of the model components are analyzed through comparing the simulation results on different models. The corresponding fingerprint features are identified on the immunityfrequency curve. Section 5 is the conclusion.

# 2. MODELS

# 2.1. The Test Fixture

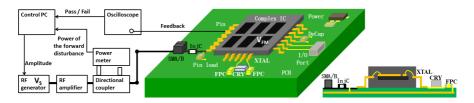

The hardware configuration of the DPI method is shown in Figure 1. A complex IC has multiple functional modules. The whole path for the EMI signal from the source to a functional module can be divided into four parts: off-board, on-board, package, and on-chip. The paper assumes that the failure of the IC is due to the fact that the amplitude of the EMI signal on a functional module is beyond the EMI threshold of that functional module. The phase of the EMI signal is irrelevant. More details about the failure criterion are given in [18].

Figure 1. Immunity measurement setup.

The off-board EMI path consists of an amplifier, a directional coupler, a SMA or SMB connector, cables and traces. Qualities of nowadays products in the RF industry make it easy to achieve the impedance match in the off-board path. The propagation changes only the phase of the EMI signal. However the phase is not important. Therefore the generator and the off-board path can be modeled with a perfect source  $V_S$  plus a resistance  $R_S$ .

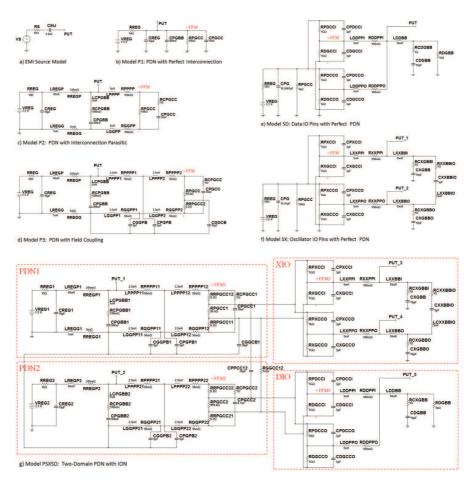

The on-board path consists of an injection capacitor and PCB traces. All of them suffer parasitic effects. Since the focus of this paper is the IC, the on-board path can be modeled with a capacitance  $C_{INJ}$ .  $V_S$ ,  $R_S$  and  $C_{INJ}$  build the model of the EMI source, depicted in Figure 2(a). Node PUT is the pin under test. The impedance at PUT toward the source is called the injection impedance  $Z_{INJ}$ . The impedance at PUT toward the DUT is the DUT is the DUT impedance  $Z_{DUT}$ .

Figure 2. Immunity models.

## 2.2. PDN Modes

A summary of model components in the PDN network is listed in Table 1. Detailed descriptions of those components are given below.

The subscript of a model element consists of a few letters indicating the nets and parts of element. As to the net, P stands for the supply, G for the ground, D for the DIO, and X for the XIO. As to the part, C stands for chip, P stands for the package, and B stands for the PCB. Moreover, there are indexes distinguishing multiple elements of the type, connecting the same nets, and between the same parts.

The precise content of a model component belongs to the topics of parameter exaction [19, 20], which is outside the scope of this paper.

| No. | Component                 | Main Elements        | Parasitic Elements     |  |

|-----|---------------------------|----------------------|------------------------|--|

| 1   | Core                      | $R_{PGCC}$           | $R_{RPGCC}$            |  |

| 2   | Chip DeCap                | $C_{PGCC}$           | $R_{CPGCC}$            |  |

| 3   | PDN Package               | Node                 | $R_{PPPP}, L_{PPPP},$  |  |

| 5   | I DIV I ackage            | Noue                 | $R_{GGPP}, L_{GGPP}$   |  |

| 4   | Board DeCap               | $C_{PGBB}$           | $R_{CPGBB}, L_{CPGBB}$ |  |

| 5   | Regulator Interconnection | Node                 | $R_{REGP}, L_{REGP},$  |  |

| 0   | Regulator interconnection | Noue                 | $R_{REGG}, L_{REGG}$   |  |

| 6   | Regulator Load Capacitor  | $C_{REG}$ NONE       |                        |  |

| 7   | Regulator                 | $R_{REG}$ NONE       |                        |  |

| 8   | Chip-board Coupling       | $C_{GGCB}$           |                        |  |

| 9   | Package-board Coupling    | $C_{PGPB}, C_{GGPB}$ |                        |  |

| 10  | Inter-domain Coupling     | $R_{GGC}$            | $_{C}, C_{PPCC}$       |  |

Table 1. List of components in PDN.

This paper uses simple elements for model components.

Mode P1 is a basic model containing the PDN of the complex IC and the board with perfect interconnections. The current consumption of a complex IC consists of leakage current, short current and switching current. All of them are proportional to the supply voltage, and thus the total current can be modeled with a resistance  $R_{PGCC}$  between the supply pin and the ground pin. A modern complex IC contains chip decoupling capacitor (DeCap). There is parasitic capacitive coupling between supply lines and the ground lines on the chip. Those two channels are modeled with a capacitance  $C_{PGCC}$ . The supply pin is normally terminated with the board DeCap, which is modeled with a capacitance  $C_{PGBB}$ . The on-board power supplier is a voltage regulator. The model of the regulator is a direct current (DC) voltage source  $V_{REG}$  plus a current-limiting resistance  $R_{REG}$ . The output of the voltage regulator is normally terminated with a load capacitor which is modeled with a capacitance  $C_{REG}$ .  $C_{REG}$ ,  $C_{PGBB}$ , and  $C_{PGCC}$ absorb high frequency noise in the PDN and they are called power capacitances.

In a typical application,  $C_{REG}$  is a few  $\mu$ F,  $C_{PGBB}$  is a few 100 nF, and  $C_{PGCC}$  is a fraction of or a few nF.  $R_{PGCC}$  is ranged from 10  $\Omega$  to 1 k $\Omega$ .  $R_{REG}$  is a few  $\Omega$ . Figure 2(b) shows the DUT model P1. In an immunity simulation, the terminal PUT in Figure 2(b) is connected to the terminal PUT in Figure 2(a). The EMI source has amplitude of  $V_S$ . The EMI voltage on the PUT is  $V_{PUT}$ . The effective EMI signal which disturbs the IC is  $V_{FM}$ . FM stands for "functional module". The impedance of a FM is called the FM impedance  $Z_{FM}$ . Model P1 is applied to study the effects of above capacitances and resistances.

Model P2 is updated from P1. It considers the parasitic effect of interconnections. The power interconnection between the IC and the voltage regulator is established with a trace (or a polygon) for the supply pins and the ground plane for the ground pins. Both of them are not perfect. Each connection is modeled with the series connection of an inductance and a resistance:  $L_{REGP}$  and  $R_{REGP}$  for the supply net, and  $L_{REGG}$  and  $R_{REGG}$  for the ground net. The chip of an IC is connected to the board through the package. A package is constructed with the lead frame and/or the bonding wire. Wires and leads carry parasitic inductance and resistances. The package is modeled with  $L_{PPPP}$  and  $R_{PPPP}$  for the supply pin, and  $L_{GGPP}$  and  $R_{GGPP}$  for the ground pin. The board DeCap has SMD package. The parasitic effect of board DeCap is modeled with an inductance  $L_{CPGBB}$  and a resistance  $R_{CPGBB}$ . The chip DeCap is distributed on the chip. The interconnection from the supply and ground pads to the DeCap carries resistance and is modeled with  $R_{CPGCC}$ . The parasitic inductance of on-chip interconnection is complex due to the complex directions of on-chip currents. This paper does not consider that inductance.

The distance between the voltage regulator and the IC is several cm and thus the corresponding  $L_{REGP}$  is tens of nH. The package inductance is a few nH. The interconnection resistance is a faction of  $\Omega$ . Figure 2(c) shows the DUT model P2. The model is applied to study the impact of each parasitic effect on the immunity.

Model P3 considers no-conductive channels in addition to the interconnections traces, wires and leads. The first channel is the field coupling between the chip and the board. It is capacitive. A PCB has small, or even no, power plane but a large ground plane. Therefore the chip-board capacitive coupling exists mainly in the ground net. The channel is modeled with a capacitance  $C_{GGCB}$ . The second channel is the capacitive between the package and the board. The channel is modeled with a capacitance  $C_{GGPB}$ . In a typical application,  $C_{GGCB}$  is tens of pF while  $C_{GGPB}$  is close to 10 pF. Figure 2(c) shows the DUT model P3. The model is applied to study the impact of each non-conductive channel on the immunity.

### 2.3. ION Models

A summary of model components in the ION is listed in Table 2. Detailed descriptions of those components are given below.

Model SD is the basic model for simulating the immunity of DIO pins. To test a data input pin, a data source is required. To test a

| No. | Component                 | Main Elements                        | Parasitic Elements   |  |

|-----|---------------------------|--------------------------------------|----------------------|--|

| 1   | Data IO (DIO) Pad         | $R_{PDCC}, R_{DGCC}$                 | $C_{PDCC}, C_{DGCC}$ |  |

| 2   | DIO Package               | Node                                 | $R_{DDPP}, L_{DDPP}$ |  |

| 3   | DIO Board Interconnection | Node                                 | $L_{DDBB}$           |  |

| 4   | DIO Load                  | $C_{DGBB}, C_{DGBB}$                 | NONE.                |  |

| 5   | Oscillator IO (XIO) Pad   | $R_{PXCC}, R_{XGCC}$                 | $C_{PXCC}, C_{XGCC}$ |  |

| 6   | XIO Package               | Node                                 | $R_{XXPP}, L_{XXPP}$ |  |

| 7   | XIO Board Interconnection | Node                                 | $L_{XXBB}$           |  |

| 8   | XIO Load                  | $C_{XGBB}$                           | $R_{CXGBB}$          |  |

| 9   | XIO Crystal               | $R_{XXBBIO}, C_{XXBBIO}, L_{XXBBIO}$ |                      |  |

Table 2. List of components in ION.

data output pin, a data receiver is required. Therefore, the DIO pins are tested in pairs: an input pin is directly connected to an output pin. An output pin has three statuses-output high, output low, and high impedance. An output pin in the high-impedance status is equivalent to an input pin. Those behaviors are realized with two resistances: one from the pad to the supply  $R_{PDCC}$  and the other from the pad to the ground  $R_{DGCC}$ . The pad of an IO is parasitically coupled to the on-chip supply and ground through mainly the electrical field. Those effects are modeled with capacitances  $C_{PDCC}$  and  $C_{DGCC}$ . The pin package is modeled with an inductance  $L_{DDPP}$  and a resistance  $R_{DDPP}$ . The load is modeled with a capacitance  $C_{DGBB}$ . IO pins are normally loaded.  $C_{DGBB}$  and  $R_{DGBB}$  are the models for alternating current (AC) load and DC load respectively. The SMD capacitor has parasitic resistance which is modeled with  $R_{CDGBB}$ . The parasitic inductance is neglected because of the board interconnection inductance  $L_{DDBB}$ . As a basic model, the supplier for the IO is modeled with a perfect PDN mode like Model P1. The pad capacitance is a few pF. The pad resistance ranges from  $10 \Omega$  to  $1 k\Omega$ .  $C_{DGBB}$  is tens of pF.  $R_{DGBB}$  is in the range of  $k\Omega$ . Model SD is shown in Figure 2(e).

Model SX is the basic model for a special IO module: the XIO module. The structure of the XIO is similar to the DIO. The main difference of the two IO structures lies in the fact that for many applications there is a resonator between the input pin and the output pin of the oscillator. The resonator is modeled with  $R_{XXBBIO}$ ,  $C_{XXBBIO}$ , and  $L_{XXBBIO}$ . Model SX is depicted in Figure 2(f). Normally,  $C_{XGBBI}$  and  $C_{XGBBO}$  share the same value. They are called the longitude foot-point capacitance [21].  $C_{XXBBIO}$  is called the transverse foot-point capacitance.

## 2.4. Model of the Whole DUT

Model PSXSD, shown in Figure 2(g), is the full DUT model. It has four blocks: two for PDN, one for DIO and one for XIO. The structures of the models come from model P3, SD and SX. The models can be used to analyze the impact between PDN domains and between the ION and the PDN.

The two PDN blocks represent two power domains. Many complex ICs have more than one power domain. Each domain has separated supply pins. The local grounds of those power domains are either directly connected or connected through the substrate. In Figure 2(g), domain 1, denoted with PDN1, is a core domain with large chip DeCap and large current while domain 2, denoted with PDN2, is a port domain with small chip DeCap and small current. Each domain has its own  $V_{FM}$ . The inter-domain connection through the substrate or the common ground is modeled with a resistance  $R_{GGCC12}$ . Besides the substrate, there is capacitive channel connecting two domains. One major origin of the channel is the electro static charge (ESD) network. The channel is modeled with a capacitance  $C_{PPCC12}$ .  $R_{GGCC12}$  is near zero for the common ground coupling and is 10 to  $100 \Omega$  for the substrate coupling.  $C_{PPCC12}$  is in the range tens of pF.

## 3. ANALYSIS METHODS

### 3.1. Immunity Calculation Method

Details of the immunity calculation method can be found in [18]. A brief description is given below. The EMI source with amplitude VS induces an EMI voltage VFM on the OCFM of the IC. TC is the transfer coefficient. As defined in (1), it is the ratio of VFM to VS. TC is obtained with AC simulation on the immunity model with a SPICE simulator. The arriving EMI voltage VFM should be below a certain threshold  $VFM_{th}$ . Once the VFM is beyond  $VFM_{th}$ , the IC is considered in the failure state. The limitation of the VFM introduces maximal allowed source amplitude  $VS_{th}$  defined in (2). The corresponding forward power of the EMI source with amplitude  $VS_{th}$  is the immunity. The forward power is obtained with (3). With the definition of a reference power  $PS_0$ , stated in (4), the immunity expression is simplified into (5). The first term in the right side of (5)is determined by the transistors. The second term of (5) is determined by the propagation network. For simplicity, this paper assumes that  $PS_{\theta}$  is independent on the frequency.

$$TC = \frac{VFM}{VS} = \frac{V_{PUT}}{VS} \frac{VFM}{V_{PUT}}$$

(1)

Progress In Electromagnetics Research, Vol. 139, 2013

$$VS_{th} = \frac{VFM_{th}}{TC} \tag{2}$$

$$\frac{PS_{th}}{dBm} = 10\log_{10}\left(\frac{VS_{th}^2/8R_S}{1\,\mathrm{mW}}\right) \tag{3}$$

$$\frac{PS_0}{\mathrm{dBm}} = 10 \log_{10} \left( \frac{VFM_{th}^2/8R_S}{1\,\mathrm{mW}} \right) \tag{4}$$

$$\frac{PS_{th}}{dBm} = \frac{PS_0}{dBm} - 20\log_{10}|TC|$$

(5)

If an IC model contains multiple VFMs, then each  $VFM_k$  introduces a  $VS_{th\_k}$  and a  $PS_{th\_k}$ . For that case, the immunity is the minimal  $PS_{th\_k}$ , as stated in (6).

$$\frac{PS_{th}}{\mathrm{dBm}} = \min_{k} \left\{ \frac{PS_{th\_k}}{\mathrm{dBm}} \right\}$$

(6)

#### **3.2.** Origins of the Immunity Features

To examining the main features of the TC, a simplified analytical expression of TC is given in (7).  $Z_{BP}$  is the impedance of a parallel branch containing the FM while  $Z_{BS}$  is the impedance of series branch containing the FM. The physical meaning of (7) is following: the DUT model is built with series and parallel connected networks.  $Z_{DUT}$  and  $Z_{INJ}$  determine the ratio of  $V_{PUT}$  to VS. The EMI current has to be divided for each parallel connection. And the EMI voltage has to be divided on each series connection.

$$TC = \frac{Z_{DUT}}{Z_{DUT} + Z_{INJ}} \frac{Z_{BS1}}{Z_{BS1}} \frac{Z_{BS2}}{Z_{BP2}} \dots \frac{Z_{FM}}{Z_{BPFM}}$$

(7)

$$TC = \begin{cases} \text{constant flat} \\ \sim f^k & \text{roll off} \\ \sim f^{-k} & \text{roll up} \\ \rightarrow 0 & \text{peak} \\ \rightarrow \infty & \text{dip} \end{cases}$$

(8)

As indicated with (7), the frequency response of TC is determined by all impedances. The expression of an impedance has frequency dependent terms and frequency independent terms. For a certain frequency interval, one term may dominate the impedance, and the impedance of a branch may be dominated by one or a few circuit elements. Therefore, for a certain frequency range, TC may respond to the frequency in a simple way. The frequency response of TC can be classified into five cases as shown in (8). The k in (8) is a positive

699

integer. The resonance in a loop formed with the circuit elements in a branch introduces  $Z_{BS}$  or  $Z_{DUT}$  to approach  $\infty$  (local maximum), and thereby a dip is shown in the immunity. The resonance of a branch introduces  $Z_{BS}$  or  $Z_{DUT}$  to approach 0 (local minimum), and thereby a peak is shown in the immunity. The origins of the flat, rolling-up and rolling-off regions can be understood easily therefore their illustration is neglected here.

## 3.3. Selection and Ordering of the Simulation Results

There are 19 components in the PDN and the ION model. Most of the components have both main elements and parasitic elements. A complete set of simulations covering all possible combinations of the model components and their elements produces huge volume of results. It is not necessary to present the whole volume of results because they carry a lot of redundant information. By carefully selection, information of N model components can be carried with N simulation results. Through elaborately ordering the comparisons between simulation results, the impact of each model component could be clearly demonstrated.

## 4. RESULTS AND DISCUSSIONS

## 4.1. EMI Source Model

A corner frequency  $f_{injRC}$  is defined in (9). In the frequency range below  $f_{injRC}$ , the impedance, which means the magnitude of the impedance here and below, of  $C_{INJ}$  is greater than  $R_S$ , and  $Z_{INJ}$  is dominated by  $C_{INJ}$ . Above  $f_{injRC}$  the impedance is dominated by  $R_S$ , see (10).

$$\frac{f_{injRC}}{0.46 \text{ MHz}} = \frac{50 \,\Omega}{R_S} \frac{6.8 \,\mathrm{nF}}{C_{INJ}} \tag{9}$$

$$Z_{INJ} \approx \begin{cases} 1/j2\pi f C_{INJ} & f < f_{injRC} \\ R_S & f_{injRC} < f \end{cases}$$

(10)

The first term in right side of (7) can be simplified into (11) or (12) depending on the relative magnitude of  $Z_{INJ}$  with respect to  $Z_{DUT}$ .

$$\frac{Z_{DUT}}{Z_{DUT} + Z_{INJ}} \approx \frac{Z_{DUT}}{Z_{INJ}} \quad Z_{DUT} \ll Z_{INJ} \tag{11}$$

$$\frac{Z_{DUT}}{Z_{DUT} + Z_{INJ}} \approx 1 \quad Z_{INJ} \ll Z_{DUT}$$

(12)

If  $Z_{DUT}$  behaves capacitively with an effective capacitance  $C_{DUT}$ , (11) can be satisfied for frequencies above  $f_{injRdutC}$ , see (13) and  $f_{injRC}$ .

If  $Z_{DUT}$  behaves inductively with an effective inductance  $L_{DUT}$ , (11) can be satisfied for frequencies between  $f_{injRC}$  and  $f_{injRdutL}$ , see (14).

$$\frac{f_{injRdutC}}{0.32\,\text{kHz}} = \frac{50\,\Omega}{R_S} \frac{10\,\mu\text{F}}{C_{DUT}} \tag{13}$$

$$\frac{f_{injRdutL}}{5\,\text{GHz}} = \frac{R_S}{50\,\Omega} \frac{1\,\text{nH}}{L_{DUT}} \tag{14}$$

If  $Z_{DUT}$  behaves resistively with an effective resistance  $R_{DUT}$ , (11) can be satisfied for frequencies below  $f_{injCdutR}$ , see (15) and  $f_{injRC}$ .

$$\frac{f_{injCdutR}}{2.3\,\mathrm{MHz}} = \frac{10\,\Omega}{R_{DUT}}\frac{6.8\,\mathrm{nF}}{C_{INJ}}\tag{15}$$

## 4.2. Simulation on PDN Model P1

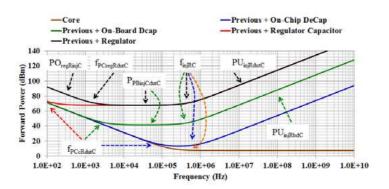

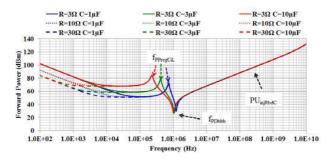

Table 3 lists a series of simulations on Model P1 in which components of a perfect PDN are one by one enabled. The corresponding simulation result is shown in Figure 3.

Table 3. Simulation setup on model P1 for Figure 3.

| Case | $R_{PGCC}$ | $C_{PGCC}$ | $C_{PGBB}$ | $C_{REG}$ | $R_{REG}$ | Curve |

|------|------------|------------|------------|-----------|-----------|-------|

| 1    | On         | Off        | Off        | Off       | Off       | Brown |

| 2    | On         | On         | Off        | Off       | Off       | Blue  |

| 3    | On         | On         | On         | Off       | Off       | Green |

| 4    | On         | On         | On         | On        | Off       | Red   |

| 5    | On         | On         | On         | On        | On        | Dark  |

Figure 3. Immunity simulation results on model P1.

The brown curve is the simulated immunity where only  $R_{PGCC}$  exists in the model. Below  $f_{injRC}$ , TC is determined by the impedance ratio of  $C_{INJ}$  to  $R_{PGCC}$ . As a result, TC increases with frequency, and the immunity decreases with frequency. Above  $f_{injRC}$ , TC is determined by the ratio of  $R_S$  to  $R_{PGCC}$ , see (16), and is thereby independent on frequency. A flat region appears in a frequency range above  $f_{injRC}$ . The corresponding immunity can be evaluated with (17). It is called the basic immunity of the supply pin, labeled with  $P_{P0}$ . It is the immunity of a naked IC without any "protection" (capacitor).

$$TC_{BP} = \frac{R_{PGCC}}{R_{PGCC} + R_S} \tag{16}$$

$$\frac{P_{P0}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20 \log_{10} \left( \frac{R_{PGCC}}{R_{PGCC} + R_S} \right) \tag{17}$$

Now refer to the red, the green and the blue curves. Enabling capacitances of model P1 increases the immunity. Among those capacitances,  $C_{REG}$  has the greatest value and thereby increases the immunity to the greatest extent. The total capacitance added into the DUT model gives  $C_{DUT}$ . At frequency above  $f_{PCcRdutC}$ , see (18), the impedance of  $C_{DUT}$  is less than  $R_{PGCC}$ , and thereby  $Z_{DUT}$  is dominated by  $C_{DUT}$ . Typically,  $f_{PCcRdutC}$  and  $f_{injRdutC}$  are much lower than  $f_{injRC}$ , therefore, in frequency region above  $f_{injRC}$ , TC is determined by the impedance ratio of  $C_{DUT}$  to  $R_S$ , see (19). A rolling-up region of +20 dB/decade appears.

$$\frac{f_{PCcRdutC}}{0.16\,\text{kHz}} = \frac{100\,\Omega}{R_{PGCC}} \cdot \frac{10\,\mu\text{F}}{C_{DUT}} \tag{18}$$

$$TC_{PUinjRdutC} = \frac{1}{j2\pi f R_S C_{DUT}}$$

(19)

Enabling  $R_{REG}$  increases the immunity further. However, the increment happens only in frequency ranging up to  $f_{PCregRdutC}$ , see (19).  $f_{PCregRdutC}$  is typically much less than  $f_{injRC}$  and  $f_{injCdutR}$ . Below  $f_{PCregRdutC}$ , the impedance of  $C_{DUT}$  is greater than  $R_{REG}$ ,  $Z_{DUT}$  is dominated by  $R_{REG}$ ,  $Z_{INJ}$  is dominated by  $C_{INJ}$ , and (11) is valid. Consequently, TC is determined by the impedance ratio of  $R_{REG}$  to  $C_{INJ}$ , see (16), and thus a rolling-off region of -20 dB/decadeappears. The corresponding immunity in the rolling-off region can be evaluated with (17).

$$\frac{f_{PCregRdutC}}{1.6\,\text{kHz}} = \frac{10\,\Omega}{R_{REG}} \cdot \frac{10\,\mu\text{F}}{C_{DUT}}$$

(20)

$$TC_{POregRinjC} = j2\pi f R_{REG} C_{INJ}$$

(21)

$$\frac{P_{POregRinjC}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\log_{10}\left(2\pi f R_{REG}C_{INJ}\right)$$

(22)

#### Progress In Electromagnetics Research, Vol. 139, 2013

In the frequencies ranging from  $f_{PCreaRdutC}$  to  $f_{injRC}$ , the impedance of  $\hat{R}_{REG}$  is greater than  $C_{DUT}$ ,  $Z_{DUT}$  is dominated by  $C_{DUT}$ , and  $Z_{INJ}$  is dominated by  $C_{INJ}$ . Consequently, TC is determined by the impedance ratio of  $C_{DUT}$  to  $C_{INJ}$ , see (23), and thus a flat region appears. The corresponding immunity in the flat region can be evaluated with (24).

$$TC_{PBinjCdutC} = \frac{C_{INJ}}{C_{DUT} + C_{INJ}}$$

(23)

$$\frac{P_{PBinjCdutC}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\log_{10}\left(\frac{C_{INJ}}{C_{DUT} + C_{INJ}}\right)$$

(24)

Off

Off

On

On

## 4.3. Simulation on PDN Model P2

On

On

On

On

$\mathbf{2}$

3

4

5

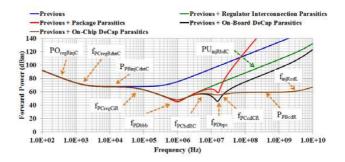

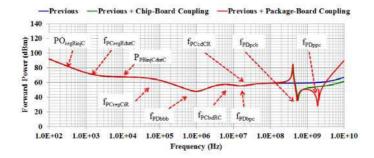

Table 4 lists a series of simulations on Model P2 in which interconnection parasitic components are one by one enabled. The corresponding simulation result is shown in Figure 4. The blue curve Figure 4 (case 1 in Table 4) is copied from the dark curve in Figure 3 (case 5 in Table 3).

| _ | Case | $R_{REGP}, L_{REGP},$ | $R_{PPPP}, L_{PPPP},$ | $R_{CPGBB}$ , | $R_{CPGCC}$   | Curve |

|---|------|-----------------------|-----------------------|---------------|---------------|-------|

|   | Case | $R_{REGG}, L_{REGG}$  | $R_{GGPP}, L_{GGPP}$  | $L_{CPGBB}$   | <i>ICPGCC</i> | Ourve |

|   | 1    | Off                   | Off                   | Off           | Off           | Blue  |

Off

On

On

On

Table 4. Simulation setup on model P2 for Figure 4.

Figure 4. Immunity simulation results on model P2.

Green

Red

Dark

Brown

Off

Off

Off

On

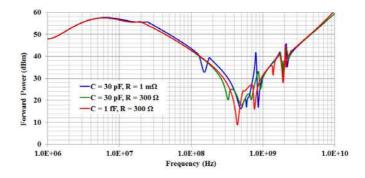

The board interconnection parasitics introduce a corner at  $f_{PCregCiR}$  and a dip at  $f_{PDbbb}$ . Before the discussion on those two frequencies, let's have a look on Figure 5. Figure 5 shows the results of a set of simulation with various  $R_{REG}$  and  $C_{REG}$ . They are simulated on model P2 where only parasitic elements  $L_{REGP}$  and  $L_{REGG}$  are enabled.  $R_{REGP}$  and  $R_{REGG}$  are set to be  $1 \text{ m}\Omega$  in that case. At  $f_{PPregCiL}$ , defined in (25), the impedance of  $L_{REGi} = L_{REGP} + L_{REGG}$  cancels the impedance of  $C_{REG}$ . Above  $f_{PPregCiL}$ , impedance of  $L_{REGi}$  shields the impedance of  $C_{REG}$ .

$$\frac{f_{PPregCiL}}{0.23 \text{ MHz}} = \sqrt{\frac{50 \text{ nH}}{L_{REGP} + L_{REGG}}} \cdot \frac{10 \,\mu\text{F}}{C_{REG}}$$

(25)

At  $f_{PDbbb}$ , defined in (26), resonance happens in the loop though  $C_{PGBB}$ ,  $L_{REGi}$  and  $C_{REG}$ , and correspondingly a dip appears in the immunity-frequency curve. Because  $L_{REGi}$  already shields the impedance of  $C_{REG}$ , therefore  $C_{REG}$  is neglected in (26).

$$\frac{f_{PDbbb}}{1\,\text{MHz}} = \sqrt{\frac{50\,\text{nH}}{L_{REGP} + L_{REGG}} \cdot \frac{500\,\text{nF}}{C_{PGBB}}} \tag{26}$$

As the frequency increases further and exceeds  $f_{PDbbb}$ , the impedance of  $C_{PGBB}$  is less than the impedance of  $L_{REG}$ .  $C_{PGBB}$ dominates  $Z_{DUT}$ . Therefore, TC is irrelevant to  $R_{REG}$  and  $C_{REG}$ .  $R_{REG}$  and  $C_{REG}$  are now ineffective. As  $C_{REG}$  becomes ineffective,  $C_{DUT}$  is the sum of  $C_{PGBB}$  and  $C_{PGCC}$ , which is roughly equal to  $C_{PGBB}$ . Therefore (18) should be updated into (27).  $f_{PDbbb}$  is much higher than  $f_{PCcRbdC}$ , so that at and above  $f_{PDbbb} Z_{DUT}$  is dominated by  $C_{DUT}$ .

$$\frac{f_{PCcRbdC}}{3.2\,\text{kHz}} = \frac{100\,\Omega}{R_{PGCC}} \cdot \frac{500\,\text{nF}}{C_{PGBB}} \tag{27}$$

Now go back to the green curve in Figure 4. When the frequency goes beyond  $f_{PCregCiR}$ , defined in (28), the existence of  $R_{REGi} = R_{REGP} + R_{REGG}$  can shield the impedance of  $C_{REG}$ , and thus dominates the DUT impedance. The injection impedance is still capacitive; therefore the immunity turns to decreases with frequency. When the frequency exceeds  $f_{PCregiRL}$ , defined in (29),  $L_{REGi}$  replaces  $R_{REGi}$  as the dominant factor for the DUT impedance, the immunity decreases further with the frequency.

$$\frac{f_{PCregCiR}}{63\,\text{kHz}} = \frac{0.25\,\Omega}{R_{PPRP} + R_{PPRP}} \cdot \frac{10\,\mu\text{F}}{C_{PPR}} \tag{28}$$

$$\frac{f_{PCregiRL}}{0.80 \text{ MHz}} = \frac{R_{REGP} + R_{REGG}}{0.25 \Omega} \cdot \frac{50 \text{ nH}}{L_{REGP} + L_{REGG}}$$

(29)

#### Progress In Electromagnetics Research, Vol. 139, 2013

Once the frequency exceeds  $f_{PDbbb}$ , the immunity increases with frequency at rate +20 dB/decade. The rolling-up region is identical to the green curve in Figure 5(a). Therefore the role of regulator interconnection parasitics is to switch the immunity from the dark curve to the red curve (both in Figure 3) at  $f_{PCregCiR}$ . With (19), the immunity of the rolling-up region can be calculated with (30).

$$\frac{P_{PUinjRbdC}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} + 20\log_{10}|2\pi f C_{PGBB}R_S| \tag{30}$$

Refer to the red curve in Figure 4. The package parasitics, the board DeCap and chip DeCap form a loop. The loop has a resonance frequency  $f_{PDbpc}$ . At  $f_{PDbpc}$ , TC approaches the local maximum, and thereby a dip appears in the immunity curve. Defining  $L_{PPG} = L_{PPPP} + L_{GGPP}$ , the resonance frequency can be calculated with (31). Beyond  $f_{PDbpc}$ , the impedance of  $L_{PPG}$  is much greater than that of  $C_{PGBB}$  and  $C_{PGCC}$ , and thereby  $Z_{DUT}$  is dominated by  $C_{PGBB}$ .  $Z_{BP}$  is dominated by  $L_{PPG}$ , and  $Z_{FM}$  is dominated by  $C_{PGCC}$ .  $f_{PDbpc}$ is above  $f_{injRdutC}$  and  $f_{injRC}$ . Therefore (11) is well satisfied. As a consequence, TC can be evaluated with (32). The immunity shows a rolling-up behavior of +60 dB/decade.

$$\frac{f_{PDbpc}}{16 \text{ MHz}} = \sqrt{\frac{10 \text{ nH}}{L_{PPG}} \cdot \frac{10 \text{ nF}}{C_{PGCC}}}$$

(31)

$$TC_{PUbdCpLcC} = \frac{1/j2\pi f C_{PGBB}}{R_S} \frac{1/j2\pi f C_{PGCC}}{j2\pi f L_{PPG}}$$

(32)

Refer to the dark curve in Figure 4. The parasitic resistance of the board DeCap  $R_{CPGBB}$  shields  $C_{PGBB}$  if the frequency is above  $f_{PCbdRC}$ , see (33). If the frequency is above  $f_{PCbdLR}$ , see (34), the board DeCap parasitic inductance  $L_{CPGBB}$  shields  $R_{CPGBB}$ . In that case,  $Z_{DUT}$  is dominated with  $L_{CPGBB}$ . Therefore the TC at frequencies

Figure 5. Supplement immunity simulation results on model P2.

above  $f_{PCbdLR}$  and  $f_{PDbpc}$  should be updated from (32) to (35). The rolling-up rate is now +20 dB/decade.

$$\frac{f_{PCbdRC}}{3.2 \,\mathrm{MHz}} = \frac{0.1 \,\Omega}{R_{CPGBB}} \cdot \frac{500 \,\mathrm{nF}}{C_{PGBB}} \tag{33}$$

$$\frac{f_{PCbdLR}}{16\,\text{MHz}} = \frac{R_{CPGBB}}{0.1\,\Omega} \cdot \frac{1\,\text{nH}}{L_{CPGBB}} \tag{34}$$

$$TC_{bcLpLcC} = \frac{L_{CPGBB}}{R_S} \frac{1/j2\pi fC_{PGCC}}{L_{PPG}}$$

(35)

Refer to the brown curve in Figure 4.  $R_{CPGCC}$  reduces the depth of the immunity dip at  $f_{PDbpc}$ . The impedance of  $R_{CPGCC}$  is greater than that of  $C_{PGCC}$  for frequencies above  $f_{PCcdRC}$ , see (36). Consequently,  $Z_{FM}$  is dominated by  $R_{CPGCC}$ , and TC in frequency range above  $f_{PCcdRC}$  and  $f_{PDbpc}$  becomes (37). It is now independent from the frequency. A flat region appears in the immunity curve. The corresponding immunity can be calculated with (38).

$$\frac{f_{PCcdRC}}{16\,\text{MHz}} = \frac{1\,\Omega}{R_{CPGCC}} \cdot \frac{10\,\text{nF}}{C_{PGCC}} \tag{36}$$

$$TC_{PBcdR} = \frac{L_{CPGBB}}{R_S} \frac{R_{CPGCC}}{L_{PPG}}$$

(37)

$$\frac{P_{PBcdR}}{\text{dBm}} = \frac{PS_0}{\text{dBm}} + 20\log_{10} \left| \frac{L_{CPGBB}}{R_S} \frac{R_{CPGCC}}{L_{PPG}} \right|$$

(38)

(38) assumes that the impedance of  $L_{CPGBB}$  is much smaller than  $R_S$ . This condition is satisfied up to frequency  $f_{PCnjRbdL}$ , defined in (39). Above  $f_{PCinjRbdL}$ , the impedance of  $L_{CPGBB}$  is greater than  $R_S$ , and the expression of TC should be modified into (40). It corresponds to a 20 dB/decade rolling-up region.

$$\frac{f_{PCinjRcdL}}{8.0\,\text{GHz}} = \frac{R_S}{50\,\Omega} \cdot \frac{1\,\text{nH}}{L_{CPGBB}} \tag{39}$$

$$TC_{PUpLccR} = \frac{R_{CPGCC}}{j2\pi f L_{PPG}}$$

(40)

Up to now, the EMI source model uses a capacitance to model the injection capacitor. However, the capacitor has parasitic resistance and inductance. The resistance is much smaller than  $R_S$  and is thereby neglectful. When the inductance  $L_{CINJ}$  is considered, (40) should be modified into (41). It still corresponds to a 20 dB/decade rolling-up region.

$$TC_{PUiLbLLpLccR} = \frac{L_{CPGBB}}{L_{CPGBB} + L_{CINJ}} \frac{R_{CPGCC}}{j2\pi f L_{PKGPG}}$$

(41)

## 4.4. Simulation on PDN Model P3

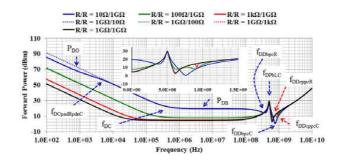

Table 5 lists a series of simulations on Model P3 in which field coupling components are one by one enabled. The corresponding simulation result is shown in Figure 6. The blue curve Figure 6 (case 1 in Table 5) is copied from the brown curve in Figure 4 (case 5 in Table 4).

Table 5. Simulation setup on model P3 for Figure 6.

| Case | $C_{GGCB}$ | $C_{GGPB}, C_{GGPB}$ | Curve |

|------|------------|----------------------|-------|

| 1    | Off        | Off                  | Blue  |

| 2    | On         | Off                  | Green |

| 3    | On         | On                   | Red   |

Figure 6. Immunity simulation results on model P3.

Refer to the green curve in Figure 6, the presence of  $C_{GGCB}$ introduces a peak and a dip near in hundreds MHz range. The origin of the peak is the resonance in the loop through  $L_{GGPP}$ ,  $R_{GGPP}$ ,  $R_{PGCC2}$ , and  $C_{GGCB}$ . The resonance induces great impedance between the chip ground and the board ground, the loop absorbs most EMI signals, and thereby the EMI signal left for  $V_{FM}$  is little. The resonance frequency is  $f_{PPpcb}$ , defined in (42). The origin of the dip is the resonance in loop through  $L_{CPGBB}$ ,  $L_{PPPP}$ ,  $R_{PGCC}$ , and the parallel connection of  $L_{GGPP}$  and  $C_{GGCB}$ .  $V_{FM}$  belongs to that loop. The resonance frequency is  $f_{PDpcb}$ , see (43).

$$\frac{f_{PPpcb}}{0.41\,\text{GHz}} = \sqrt{\frac{5\,\text{nH}}{L_{GGPP}} \cdot \frac{30\,\text{pF}}{C_{GGCB}}} \tag{42}$$

$$\frac{f_{PDpcb}}{0.58 \text{ GHz}} = \sqrt{\frac{2.5 \text{ nH}}{L_{GGPP} \parallel L_{PPPP}} \cdot \frac{30 \text{ pF}}{C_{GGCB}}}$$

(43)

Refer to the red curve in Figure 6, the presence of  $C_{PGPB}$  and  $C_{GGPB}$  introduce respectively two dips above 1 GHz. One is induced by the resonance in the loop through  $L_{GGPP2}$ ,  $R_{PGCC}$ ,  $L_{PPPP}$ , and the parallel connection of  $L_{GGPP1}$  and  $C_{PGPB}$ . The other is induced by the resonance in the loop through  $L_{PPPP2}$ ,  $R_{PGCC}$ ,  $L_{GGPP}$ , and the parallel connection of  $L_{CPGBB} + L_{PPPP1}$  and  $C_{PGPB}$ . Both loops contain  $V_{FM}$ . Their resonance frequencies are given with (44) and (45) respectively.

$$\frac{f_{PDppb1}}{1.6 \text{ GHz}} = \sqrt{\frac{2 \text{ nH}}{L_{PCBLOOP}} \cdot \frac{5 \text{ pF}}{C_{PBCLOOP}}} \\

\begin{cases}

L_{PCBLOOP} = \left(L_{PPPP} + L_{CPGBB} + \frac{L_{GGPP}}{2}\right) \parallel \frac{L_{GGPP}}{2} \\

C_{PBCLOOP} = C_{PGPB}

\end{cases} (44) \\

\frac{f_{PDppb2}}{1.4 \text{ GHz}} = \sqrt{\frac{2.5 \text{ nH}}{L_{PPBLOOP}} \cdot \frac{5 \text{ pF}}{C_{PPBLOOP}}} \\

\begin{cases}

L_{PPBLOOP} = \left(L_{PPPP} + \frac{L_{GGPP}}{2}\right) \parallel \left(\frac{L_{GGPP}}{2} + L_{CPGBB}\right) \\

C_{PPCLOOP} = C_{PGPB}

\end{cases} (45)$$

#### 4.5. Simulations on Model SD

Table 6 lists a series of simulations on Model SDin which various states of the output pin are selected. The corresponding simulation result is shown in Figure 7.

| Case | Output State | $R_{PDCCO}$         | $R_{DGCCO}$         | Curve        |

|------|--------------|---------------------|---------------------|--------------|

| 1    | Strong High  | $10\Omega$          | $1\mathrm{G}\Omega$ | Blue         |

| 2    | Medium High  | $100\Omega$         | $1\mathrm{G}\Omega$ | Green        |

| 3    | Weak High    | $1\mathrm{k}\Omega$ | $1\mathrm{G}\Omega$ | Red          |

| 4    | Strong Low   | $1\mathrm{G}\Omega$ | $10\Omega$          | Dotted Blue  |

| 5    | Medium Low   | $1\mathrm{G}\Omega$ | $100\Omega$         | Dotted Green |

| 6    | Weak Low     | $1\mathrm{G}\Omega$ | $1\mathrm{k}\Omega$ | Dotted Red   |

| 7    | Hi-Z         | $1\mathrm{G}\Omega$ | $1\mathrm{G}\Omega$ | Dark         |

Table 6. Simulation setup on model SD for results in Figure 7.

Let's consider the state of output Low first. At low frequency, the pad capacitances (in pF range) and the interconnection inductances are inactive, and TC can be expressed with (46). The corresponding immunity is given in (47). The TC has a corner frequency  $f_{DC}$ , stated in (48). Below  $f_{DC}$ , TC is proportional to frequency, and the

Figure 7. Immunity simulation results on model SD.

immunity has rolling-off behavior. Beyond  $f_{DC}$ ,  $C_{INJ}$  is neglectful, TC is simplified into (49) and the immunity can be expressed as (50). It corresponds to a flat region in the immunity-frequency curve.

$$TC_{DO} = \frac{R_{DGCCO} \parallel R_{DGBB}}{\frac{1}{j2\pi f C_{INJ}} + R_{DGCCO} \parallel R_{DGBB} + R_S}$$

(46)

$$\frac{P_{DO}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\log_{10}|TC_{DO}| \tag{47}$$

$$\frac{J_{DC}}{0.47 \,\mathrm{MHz}} = \frac{50 \,\Omega}{R_{DGCCO} \parallel R_{DGBB} + R_S} \cdot \frac{6.8 \,\mathrm{nF}}{C_{INJ}} \tag{48}$$

$$TC_{DB} = \frac{R_{DGCCO} \parallel R_{DGBB}}{R_{DGCCO} \parallel R_{DGBB} + R_S}$$

(49)

$$\frac{P_{DB}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\mathrm{log}_{10} \left| \frac{R_{DGCCO} \parallel R_{DGBB}}{R_{DGCCO} \parallel R_{DGBB} + R_S} \right| \quad (50)$$

As the frequency increases further, the EMI may induce resonance in the ION, and thereby immunity peaks and dips appear. The peak is due to the resonance in the load between  $L_{DDBB}$  and  $C_{DGBB}$ . The resonance frequency is  $f_{DPbLC}$ , stated in (51). Please note, the impedance of  $R_{DGBB}$  at frequency near GHz is much higher than that of  $C_{DGBB}$ , therefore  $R_{DGBB}$  is neglectful.

$$\frac{f_{DPbLC}}{0.50 \text{ GHz}} = \sqrt{\frac{10 \text{ nH}}{L_{DDBB}} \cdot \frac{10 \text{ pF}}{C_{DGBB}}}$$

(51)

The pad capacitances of the input pin and output pin to the supply net and to the ground net are almost the same, and therefore this paper uses  $C_{DPAD}$  to present them. The package inductance of DIO pins are also almost the same, and therefore this paper uses  $L_{DDPP}$ to present them. The frequency where the impedance of  $C_{DPAD}$  and the impedance of  $R_{DGCCO}$  are equal in magnitude is  $f_{DCpadRC}$ , defined in (52), which indicates that in the state of strong Low,  $R_{DGCCO}$  will dominate the impedance between the output pad and the ground up to 5 GHz. Consequently, the immunity dip can be induced by the resonance in the loop through  $C_{DGBB}$ ,  $L_{DDBB}$ ,  $L_{DDPPO}$ , and  $R_{DGCCO}$ . The location of the dip is  $f_{DDbpcR}$ , stated in (53). Another loop is through  $R_{DGCCO}$ ,  $L_{DDPPO}$ ,  $L_{DDPPI}$ , and the parallel connection of  $C_{PDCCI}$  and  $C_{DGCCI}$ . The resonance frequency is  $f_{DDcppcR}$ , stated in (54). Due to the bypass effect of  $C_{DGBB}$ , which reduces the effective loop capacitance, the exact dip location is little bit higher than  $f_{DDcppcR}$ .

$$\frac{f_{DCpadRC}}{5.3\,\text{GHz}} = \frac{10\,\Omega}{R_{DGCCO}} \cdot \frac{3\,\text{pF}}{C_{DPAD}}$$

(52)

$$\frac{f_{DDbpcR}}{0.41 \text{ GHz}} = \sqrt{\frac{15 \text{ nH}}{L_{DDBB} + L_{DDPPO}}} \cdot \frac{10 \text{ pF}}{C_{DGBB}}$$

(53)

$$f_{DDcnncR} = \sqrt{\frac{10 \text{ nH}}{6 \text{ pF}}}$$

(53)

$$\frac{f_{DDcppcR}}{0.65\,\text{GHz}} = \sqrt{\frac{10\,\text{nH}}{2L_{DDPP}}} \cdot \frac{6\,\text{pF}}{2C_{DPAD}} \tag{54}$$

Moreover, (52) indicates that in the medium and weak Low state,  $C_{DPAD}$  will dominate the impedance when the frequency is close to 1 GHz, and thereby  $R_{DGCCO}$  is neglectful for that frequency range. It is now not necessary for the resonant loop to include  $R_{DGCCO}$ . There are two loops whose resonances introduce immunity dips. The first one is longitude (from the PCB to the pad) which goes through  $C_{DGBB}$ ,  $L_{DDBB}$ , and the parallel connection of the packages and pads of the two DIO pins. The resonance frequency is  $f_{DDbpcC}$ , given in (55). The second one is transverse (from one pad to the other pad) which goes throughinput pad, the input package, the output package, and the output pad. The resonance frequency is  $f_{DDcppcC}$ , given in (56). When the output pin is in Hi-Z state, the structures of the two pins are identical, there is no transverse loop resonance, and therefore there is no dip at  $f_{DDcppcC}$  in the dark curve in Figure 7.

$$\frac{f_{DDbpcC}}{0.61 \,\mathrm{GHz}} = \sqrt{\frac{12.5 \,\mathrm{nH}}{L_{DDBB} + \frac{L_{DDPP}}{2}}} \cdot \frac{5.5 \,\mathrm{pF}}{\frac{4C_{PAD}C_{DGBB}}{4C_{PAD} + C_{DGBB}}}$$

(55)

$$\frac{f_{DDcppcC}}{0.92 \,\mathrm{GHz}} = \sqrt{\frac{10 \,\mathrm{nH}}{2L_{DDPP}}} \cdot \frac{3 \,\mathrm{pF}}{C_{PAD}}$$

(56)

The output pin can be set as High or Low. When the output is High, the DC channel between the pad and the ground is  $R_{PDCC} + R_{REG}$ . When the output is low, the DC channel between the pad and the ground is  $R_{DGCC}$ . The difference of the two states is  $R_{REG}$ .

Therefore the simulation results for those two states are distinguishable in the low frequency range. If the frequency is sufficiently high, say above  $f_{DCpadRpdnC}$ , see (57), the impedance between the pad (state High) and the ground will be dominated by  $R_{PDCC}$ , and therefore its immunity will be indistinguishable from that of the state Low.

$$\frac{f_{DCpadRpdnC}}{0.15 \,\mathrm{kHz}} = \frac{10\,\Omega}{R_{PDCC}} \cdot \frac{10.5\,\mu\mathrm{F}}{C_{PG}} \tag{57}$$

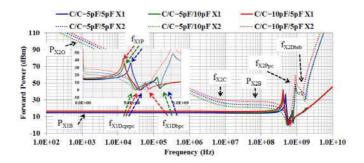

## 4.6. Simulations on Model SX

Table 7 lists a series of simulations on Model SX in which various values are assigned to the foot-point capacitances. In the first three cases, the PUT is the oscillator input pin (X1). In the later three cases, the PUT is the oscillator output pin (X2). The corresponding simulation result is shown in Figure 8.

Table 7. Simulation setup on model SX for results in Figure 8.

| Case | PUT | $C_{XGBBI}$     | $C_{XGBBO}$     | $C_{XXBBIO}$    | Curve        |

|------|-----|-----------------|-----------------|-----------------|--------------|

| 1    | X1  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | Blue         |

| 2    | X1  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | $10\mathrm{pF}$ | Green        |

| 3    | X1  | $10\mathrm{pF}$ | $10\mathrm{pF}$ | $5\mathrm{pF}$  | Red          |

| 4    | X2  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | Dotted Blue  |

| 5    | X2  | $5\mathrm{pF}$  | $5\mathrm{pF}$  | $10\mathrm{pF}$ | Dotted Green |

| 6    | X2  | $10\mathrm{pF}$ | $10\mathrm{pF}$ | $5\mathrm{pF}$  | Dotted Red   |

Figure 8. Immunity simulation results on model SX.

Let's consider the case that the PUT is pin X1 first.  $C_{INJ}$  dominates the injection impedance for frequency up to  $f_{xinjCR}$ . According to (58),  $f_{xinjCR}$  is typically near 1 GHz. In the low frequency range, inductances are ineffective, and thereby TC can be expressed with (59). The corresponding immunity, see (60), is called the base immunity of the oscillator input pin. The pad capacitances of pin X1 and pin X2 to the supply net and to the ground net are almost the same, and therefore the paper uses  $C_{XPAD}$  to present them.

$$\frac{f_{XinjCR}}{0.5\,\text{GHz}} = \frac{50\,\Omega}{R_S} \cdot \frac{6.8\,\text{pF}}{C_{INJ}} \tag{58}$$

$$TC_{X1B} = \frac{C_{INJ}}{C_{INJ} + C_{XGBBI} + 2C_{XPAD}}$$

(59)

$$\frac{P_{X1B}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\mathrm{log}_{10} \left| \frac{C_{INJ}}{C_{INJ} + C_{XGBBI} + 2C_{XPAD}} \right| \quad (60)$$

There is an obvious dip near 0.5 GHz in all three curves. At  $f_{XIP}$ , the imagine part of the impedance at node PUT toward the board is zero, i.e., impedance of  $L_{XXBBI}$  cancels the imagine part of the impedance of network right to  $L_{XXBBI}$ . Most EMI current at node PUT flows toward the board, and little current flows to pad X1. Therefore the DUT shows a peak immunity here.  $f_{XIP}$  can be roughly evaluated with (61).

$$\frac{f_{X1P}}{0.55\,\text{GHz}} = \sqrt{\frac{10\,\text{nH}}{L_{XXBBI}} \cdot \frac{8.3\,\text{pF}}{C_{XGBBI} + C_{XXBBIO}}} \tag{61}$$

There is a dip at slightly above 0.5 GHz in all three curves. The location of the dip is sensitive to the value of  $C_{XXBBIO}$  and is insensitive to the value of  $C_{XGBBI}/C_{XGBBO}$ . The dip is due to the resonance in the transverse loop through input pad, the input package, the resonance, the output package, and the output pad. The resonance frequency,  $f_{X1Dcurpc}$ , of the loop is given in (62).

$$\frac{f_{X1\,Dcprpc}}{0.62\,\text{GHz}} = \sqrt{\frac{35\,\text{nH}}{L_{X1\,TLOOP}} \cdot \frac{1.88\,\text{pF}}{C_{X1\,TLOOP}}} \\

\begin{cases}

L_{X1\,TLOOP} = 2L_{XXPP} + 2L_{XXBB} + L_{XXBBIO} \\

C_{X1\,TLOOP} = \left(2\frac{1}{2C_{XPAD}} + \frac{1}{C_{XXBBIO}}\right)^{-1}

\end{cases} (62)$$

There is a dip at near 1 GHz in all three curves. The location of the dip is sensitive to the value of  $C_{XGBBI}/C_{XGBBO}$  and is insensitive to the value of  $C_{XXBBIO}$ . The dip is due to the resonance in the longitude loop through input pad, the input package, and the input load. The resonance frequency,  $f_{X1Dbpc}$ , of the loop is given in (63).

$$\frac{f_{X1Dbpc}}{0.79\,\text{GHz}} = \sqrt{\frac{15\,\text{nH}}{L_{X1LLOOP}}} \cdot \frac{2.72\,\text{pF}}{C_{X1LLOOP}}$$

Progress In Electromagnetics Research, Vol. 139, 2013

$$\begin{cases} L_{X1LLOOP} = L_{XXPP} + L_{XXBB} \\ C_{X1LLOOP} = \left(\frac{1}{2C_{XPAD}} + \frac{1}{C_{XGBB}}\right)^{-1} \end{cases}$$

(63)

Now consider the case that PUT is pin X2. EMI injected on X2 can also induce the resonances of (62) and (63). Therefore there are corresponding dips at those frequencies. However the injection on X2 results in a peak near 1 GHz and an additional dip above 1 GHz.

Refer to the peak. At  $f_{X2Ppc}$ , the imagine part of the impedance at node PUT toward the chip is zero, most EMI current at node PUT flows toward pad X2, and little current flows to pad X1. Therefore the DUT shows a peak immunity here.  $f_{X2Ppc}$  can be roughly evaluated with (64).

$$\frac{f_{X2Ppc}}{0.92\,\text{GHz}} = \sqrt{\frac{5\,\text{nH}}{L_{XXPPO}} \cdot \frac{6\,\text{pF}}{2C_{XPAD}}} \tag{64}$$

Refer to the dip. At  $f_{X2Dbrb}$ , a resonance happens in the loop through  $C_{XGBBI}$ ,  $C_{XXBIO}$ , and  $C_{XGBBO}$ . The corresponding frequency is given in (65).

$$\frac{f_{X2Dbrb}}{1.7\,\text{GHz}} = \sqrt{\frac{5\,\text{nH}}{L_{CXXBBIO}}} \cdot \left(\frac{5\,\text{pF}}{C_{XXBIO}} + \frac{5\,\text{pF}}{C_{XGBBO}} + \frac{5\,\text{pF}}{C_{XGBBI}}\right) \quad (65)$$

At frequencies below  $f_{X2C}$ , see (66),  $R_{PXCCO}$  dominates the voltage at the PUT. The EMI signal at the PUT has to go through CXXBIO to reach pad XI. Therefore the TC can be expressed with (67). The corresponding immunity, see (68), is called the base immunity of the oscillator output pin.

$$\frac{f_{X2C}}{10 \text{ MHz}} = \frac{1000 \,\Omega}{R_{PXCCO}} \cdot \frac{16 \,\mathrm{pF}}{2C_{XPAD} + C_{XGBBO} + C_{XXBBIO}} \tag{66}$$

$$TC_{X2O} = \frac{J^{Z\pi} J C_{INJ} R_{PXCCOC} C_{XXBBIO}}{C_{XXBBIO} + C_{XGBBI} + 2C_{XPAD}}$$

(67)

$$\frac{P_{X2O}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20\log_{10} |TC_{XinjCbCcCrC}|$$

(68)

At frequencies above  $f_{X2CpadRC}$ , see (69),  $R_{PXCCO}$  is ineffective. The EMI signal at the PUT has to go through  $C_{XXBIO}$  to reach pad XI. Therefore the TC can be expressed with (70). The corresponding immunity, see (71), is called the base immunity of the oscillator output pin.

$$\frac{f_{X2CpadRC}}{53 \text{ MHz}} = \frac{1000 \,\Omega}{R_{PXCCO}} \cdot \frac{3 \,\mathrm{pF}}{C_{XPAD}} \tag{69}$$

$$TC_{X2B} = \frac{C_{INJ}C_{XXBBIO}}{\left(2C_{XPAD} + C_{XGBB} + C_{XXBBIO}\right)^2}$$

(70)

$$\frac{P_{X2B}}{\mathrm{dBm}} = \frac{PS_0}{\mathrm{dBm}} - 20 \log_{10} |TC_{XinjCbCcCrC}|$$

(71)

The dips due to the resonances in ION network of the DIO pin the XIO pin are called foot-point dips. Their locations are labeled with  $f_{fpD}$  for DIO network,  $f_{fpX}$  for XIO network, and are generally labeled with  $f_{fp}$  for any ION network. (52)–(55), (61), (62), and (64) are all expressions for  $f_{fp}$ .

#### 4.7. Simulations on Model PSXSD

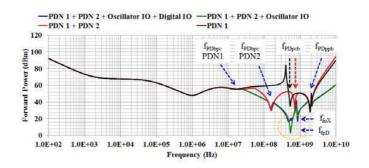

Table 8 lists a series of simulations on Model PSXSD where the PUT is supply pin (PUT1) of the first power domain(PDN1). PUT1 is the same PUT in simulations on model P1–P3. In that series, the second power domain (PDN2), the XIO block, and the DIO block are included one by one. The corresponding simulation result is shown in Figure 9.

Compare the red curve with the black curves in Figure 9. The greatest change on the immunity is the dip at  $f_{PDbpc2}$  ( $f_{PDbpc}$  of

Table 8. Simulation setup on model PSXSD for results in Figure 9.

| Case | PDN1     | PDN2     | DIO      | XIO      | Curve |

|------|----------|----------|----------|----------|-------|

| 1    | Included | Excluded | Excluded | Excluded | Black |

| 2    | Included | Included | Excluded | Excluded | Red   |

| 3    | Included | Included | Included | Excluded | Green |

| 4    | Included | Included | Included | Included | Blue  |

Figure 9. Immunity simulation results on model PSXSD, supply pin of PDN1.

#### Progress In Electromagnetics Research, Vol. 139, 2013

PDN2). The origin of the dip is the following: The EMI signal is coupled to PDN2 and induces the resonance of PDN2 at  $f_{PDbpc2}$ . Moreover, the introduction of PDN2 reduces the ground inductance and therefore shifts  $f_{PDbpc1}$  ( $f_{PDbpc}$  of PDN1) to higher frequency.

Compare the green curve with the blue curve in Figure 9. The introduction of the XIO block brings a further dip at  $f_{fp}$ . The origin is that the EMI signal is coupled into the XIO block and induces resonance at  $f_{fpX}$  in that block.

Compare the blue curve with the green curve in Figure 9. The presence of DIO block introduces resonance in  $f_{fpD}$ .  $f_{fpX}$  is close to  $f_{fpD}$ , therefore the immunity dip structure changes.

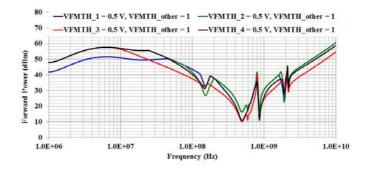

The immunity curves in Figure 9 are calculated under the condition that all functional modules have the same  $VFM_{th}$ . In reality, each functional module has its own  $VFM_{th}$  which is different from others. Some module might be very sensitive to EMI and thereby has low VFM<sub>th</sub>. Figure 10 shows the cases that the  $VFM_{th}$  of one module is only half of other three modules. Comparing the red curve with others, one can immediately observe that the selection of threshold values influence considerably the simulation results. The two immunity dips labeled with  $f_{PDbpc}$  almost disappear in the red curve.

Figure 10. Immunity simulation results on model PSXSD, threshold effects.

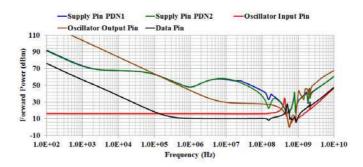

Figure 11 shows simulation results over three different interdomain coupling configurations. Refer to the red and the blue curves, if the inter-domain coupling is broken, i.e., the two power domains are connected through only the resistive substrate, then the dip structure in the near GHz range will be greatly simplified. That is because the resonances in the second power domain cannot influence the first power domain.

Comparing the green curve with the blue curve, one can observe that the substrate model plays an important role on the dip  $f_{PDbpc2}$ .

Figure 11. Immunity simulation results on model PSXSD, interdomain coupling effects. C stands for  $C_{PPCC}$ ; R stands for  $R_{GGCC}$ .

Figure 12. Immunity simulation results on model PSXSD, various pins.

When the common ground model is replaced with a resistive substrate model, there will be no channel for the resonance of the second power domain at  $f_{PDbpc2}$ . Be coupled to the first power domain. However, resonances at higher frequencies  $(f_{PDpcb}, f_{PDppb}, f_{fpD})$  can reach the first power domain through the capacitive coupling  $(C_{PPCC})$  between the power grids of the two domains reduces.

$$\frac{f_{PPpccp}}{0.29\,\text{GHz}} = \sqrt{\frac{10\,\text{nH}}{2L_{GGPP}} \cdot \frac{30\,\text{pF}}{C_{PPCC}}} \tag{72}$$

Refers to the green and the red curves in Figure 11,  $C_{PPCC}$  itself introduces a dip (near 300 MHz in Figure 11). The dip location can be estimated with (72). However, the dip is eliminated when the substrate resistance model is replaced with a common ground model. Shortening the grounds of the two domains damped the corresponding loop resonance across  $C_{PPCC}$ .

| Supply $P_{P0}$ Basic immunity(1)Supply $P_{POregRinjC}$ Regulator rolling-offkHz(2)Supply $f_{PCregRdutC}$ Regulator cornerkHz(2)Supply $P_{PBinjCdutC}$ Regulator flatkHz(2)Supply $P_{PBinjCdutC}$ Regulator flatkHz(2)Supply $f_{PCregCiR}$ Regulator trace cornerkHz(2)Supply $f_{PDbbb}$ Board Decap dipMHz(2)Supply $P_{PUinjRcC}$ Board Decap rolling-upMHz(3)Supply $P_{PBcdR}$ Chip Decap flatGHz(3)DIO $P_{DO}$ Pad driver rolling-offkHz(4)DIO $f_{DC}$ Pad driver cornerMHz(4)  |        |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| Supply $P_{POregRinjC}$ Regulator rolling-offkHz(2Supply $f_{PCregRdutC}$ Regulator cornerkHz(2Supply $P_{PBinjCdutC}$ Regulator flatkHz(2Supply $P_{PBinjCdutC}$ Regulator flatkHz(2Supply $f_{PCregCiR}$ Regulator trace cornerkHz(2Supply $f_{PDbbb}$ Board Decap dipMHz(2Supply $f_{PDbbb}$ Board Decap dipMHz(3Supply $P_{PUinjRcC}$ Board Decap flatGHz(3DIO $P_{DO}$ Pad driver rolling-offkHz(4DIO $f_{DC}$ Pad driver cornerMHz(4                                                   | PUT    | Eq.  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supply | (17) |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supply | (22) |

| $\begin{array}{c} \text{Supply}  f_{PCregCiR} & \text{Regulator trace corner} & \text{kHz} & (2) \\ \text{Supply}  f_{PDbbb} & \text{Board Decap dip} & \text{MHz} & (2) \\ \text{Supply}  f_{PDbbb} & \text{Board Decap rolling-up} & \text{MHz} & (3) \\ \text{Supply}  P_{PBcdR} & \text{Chip Decap flat} & \text{GHz} & (3) \\ \text{DIO}  P_{DO} & \text{Pad driver rolling-off} & \text{kHz} & (4) \\ \text{DIO}  f_{DC} & \text{Pad driver corner} & \text{MHz} & (4) \\ \end{array}$ | Supply | (20) |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                         | Supply | (24) |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                         | Supply | (28) |

| Supply $P_{PBcdR}$ Chip Decap flatGHz(3)DIO $P_{DO}$ Pad driver rolling-offkHz(4)DIO $f_{DC}$ Pad driver cornerMHz(4)                                                                                                                                                                                                                                                                                                                                                                        | Supply | (26) |

| $\begin{array}{cccc} DIO & P_{DO} & Pad driver rolling-off & kHz & (4) \\ DIO & f_{DC} & Pad driver corner & MHz & (4) \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                       | Supply | (30) |

| DIO $f_{DC}$ Pad driver corner MHz (4                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supply | (38) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIO    | (47) |

| DIO $P_{DB}$ Pad driver flat MHz (5                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DIO    | (48) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIO    | (50) |

| DIO $f_{DPbLC}$ Load peak GHz (5                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DIO    | (51) |

| XI $P_{X1B}$ Pad cap flat MHz (6                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XI     | (60) |

| XI $f_{X1P}$ Load peak GHz (6                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XI     | (61) |

| XO $P_{X2O}$ Pad board rolling-off kHz (6                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XO     | (68) |

| XO $f_{X2C}$ Pad board corner MHz (6                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XO     | (66) |

| XO $P_{X2B}$ Pad board flat MHz (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XO     | (71) |

| XO $f_{X2Ppc}$ Pad package peak GHz (6                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XO     | (64) |

Table 9. Summary of critical features of immunity, basic.

Figure 12 compares the simulated immunity of various types of pins. The immunity of XI pin has a simple frequency behavior. From low frequency to high frequency, the immunity curve is firstly a flat region and then dips. The immunity of the XO pin and the DIO pin behave similarly. From low frequency to high frequency, the immunity is firstly a 20 dB/decade rolling-off region, then a flat region, and lastly dips. The immunity of XO pin is much higher than of DIO, because the injection capacitor for XO is smaller than that of DIO and, for XO, there is a resonator separating the PUT and the  $V_{FM}$ . The immunity of the supply pins has the most complicated frequency behavior. From low frequency to high frequency, the immunity curve is firstly a  $20 \, dB/decade$  rolling-off region, then a flat region, the dip due to the regulator-resonance, the dip due to the resonance in PDN1, the dip due to the resonance in PDN2, and lastly dips near 1 GHz range. The two supply pins have similar immunity behaviors. Their discrepancy in 100 MHz range is due to the difference in  $C_{PGCC}$ . Immunity of all types of pins share dips at frequencies near 1 GHz. The inter-block coupling makes it possible that injection EMI on the pin of one block induces the resonance in other blocks. Therefore, the immunity dips of different types of pins are correlated.

| Network | Label          | Resonance Loop             | Position | Eq.         |

|---------|----------------|----------------------------|----------|-------------|

| PDN     | $f_{PDbpc}$    | Package chip package       | MHz      | (31)        |

| PDN     | $f_{PDpcb}$    | Package chip-board         | GHz      | (43)        |

| PDN     | $f_{PDppb}$    | Package package-board      | GHz      | (44) $(45)$ |

| DIO     | $f_{DDbpc}$    | Single-pin package pad     | GHz      | (53) $(55)$ |

| DIO     | $f_{DDcppc}$   | Inter-pin package pad      | GHz      | (54) $(56)$ |

| XIO     | $f_{X1Dcprpc}$ | Inter-pin load package pad | GHz      | (62)        |

| XIO     | $f_{X1Dbpc}$   | Single-pin package pad     | GHz      | (63)        |

| XIO     | $f_{X2Dbrb}$   | Inter-pin load             | GHz      | (65)        |

Table 10. Summary of critical features of immunity, common dips.

## 5. CONCLUSION

Table 9 summarizes the important features of the immunity for each type of pins. Table 10 summarizes the important dips that may appear in the immunity of all type of pins. The order of magnitude of the EMI frequency which is near to a feature is given as the position of the feature.

The immunity of a pin of a complex IC is characterized with rolling-off region, flat region, rolling-up regions. Those regions are separated with corner frequencies. The immunity level of regions and the values of corner frequencies are determined with corresponding model elements. Moreover, an immunity curve has dips. The origin of a dip is the resonance in the corresponding current loop. The dip location is the resonance frequency. The resonance is determined with the effective loop inductance and the effective loop capacitance. The dips can be a common structure for different types of pin. With equations, this paper gives the responsible model components for those regions and frequencies.

### ACKNOWLEDGMENT

This work was supported by the National Natural Science Foundation of China under Grant no. 61007026 and Scientific Research Foundation for Young Teacher by Sun Yat-sen University under Grant no. 111gpy74.

### REFERENCES

1. "Integrated Circuits — Measurement of electromagnetic immunity, 150 kHz to 1 GHz — Part 1: General conditions and definitions," IEC Standard IEC 62132-1, 2006.

- 2. "EMC IC modeling Part 4: Models of integrated circuits for EMI behavioural simulation, conducted immunity modelling (ICIM-CI)," IEC Standard Proposal, Future IEC 62433-4, 2012.

- Richardson, R. E., V. G. Puglielli, and R. A. Amadori, "Microwave interference effect in bipolar transistor," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 17, 216–219, November 1975.

- 4. Joester, M., F. Klotz, W. Pfaff, and T. Steinecke, "Generic IC EMC test specification," German Electrical and Electronic Manufactures' Association, Frankfurt, Germany, 2010.

- 5. "Integrated circuits Measurement of electromagnetic immunity, 150 kHz to 1 GHz — Part 4: Direct RF power injection method," IEC Standard IEC 62132-4, 2006.

- 6. Camp, M., H. Gerth, H. Garbe, and H. Haase, "Predicting the breakdown behavior of microcontrollers under EMP/UWB impact using a statistical analysis," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 46, 368–379, February 2004.

- Stievano, I., E. Vialardi, and F. Canavero, "Behavioral macromodels of digital integrated circuits for RF immunity prediction," *Proceedings of 18th International Zurich Symposium* on Electromagnetic Compatibility, 5–8, Zurich, 2007.

- 8. Ceperic, V. and A. Baric, "Modelling of electromagnetic immunity of integrated circuits by artificial neural networks," *Proceedings* of 20th International Zurich Symposium on Electromagnetic Compatibility, 373–376, Zurich, 2009.

- 9. Takahashi, E., O. Shibata, Y. Fukumoto, T. Yaneda, and H. Benno, "Evaluation of LSI immunity to noise using equivalent internal impedance model," *Proceedings of EMC Europe International Symposium on Electromagnetic Compatibility of Integrated Circuits*, September 2002.

- 10. Baffreau, S. and E. Sicard, "On the modeling of microcontrollers immunity to radio frequency interference," *Proceedings of EMC COMPO International Workshop on Electromagnetic Compatibility of Integrated Circuits*, November 2002.

- 11. Baffreau, S., S. Bendhia, M. Mamdani, and E. Sicard, "On the susceptibility of micro-controller to radio frequency interference," *Proceedings of EMC COMPO International Workshop on Electromagnetic Compatibility of Integrated Circuits*, March 2004.

- 12. Ichikawa, K., M. Inagaki, Y. Sakura, I. Iwase, M. Nagata, and O. Wada, "Simulation of integrated circuit immunity with LECCS model," *Proceedings of 17th International Zurich Symposium on*

Electromagnetic Compatibility, 308–311, February 2006.

- 13. Boyer, A., S. Bendhia, and E. Sicard, "Modelling of a direct power injection aggression on a 16 bit microcontroller input buffer," *Proceedings of EMC COMPO International Workshop on Electromagnetic Compatibility of Integrated Circuits*, Torino, 2007.